# DDXi-2161 / DDXi-2101

# 2/2.1 Channel Integrated Audio Controller and Power Output

#### **FEATURES**

- 3 Power Output Configurations

- DDX<sup>®</sup> Mono-Mode:

- o **DDXi-2161:** 1 x 160 W 3 $\Omega$  < 10% THD o **DDXi-2101:** 1 x 120 W 4 $\Omega$  < 10% THD

- DDX Full-Bridge Mode:

- 0 **DDXi-2161**: 2 x 80 W  $6\Omega$  < 10% THD 0 **DDXi-2101**: 2 x 60 W  $8\Omega$  < 10% THD

- Binary 2.1 Mode:

- o **DDXi-2161**: 2 x 35 W  $4\Omega$  +1 x 80 W  $6\Omega$  < 10% THD

- o **DDXi-2101**: 2 x 30 W  $4\Omega$  +1 x 60 W  $8\Omega$  < 10% THD

- Power SO-36 Package

- 2/2.1 Channels of 24-Bit DDX®

- 99dB SNR and Dynamic Range

- 32kHz to 192kHz Input Sample Rates

- Digital Gain/Attenuation +48dB to -80dB in 0.5dB steps

- 4 24-bit Programmable Biquads (EQ) per Channel

- I<sup>2</sup>C Control

- 2-Channel I<sup>2</sup>S Input Data Interface

- Each Channel and Master Gain/Attenuation, Soft and Hard Mute

- Individual Channel Volume and EQ Bypass

- Bass/Treble Tone Control

- Dual Independent Programmable Limiters/Compressors

- Automodes™

- \* 31 Preset EQ Curves

- \* 15 Preset Crossover Settings

- \* Auto Volume Controlled Loudness

- \* 3 Preset Volume Curves

- \* 2 Preset Anti-Clipping Modes

- \* Preset Night-time Listening Mode

- Input and Output Channel Mapping

- AM Noise Reduction and

Shifting I

- PWM Frequency Shifting ModesSoft Volume Update and Muting

- Auto Zero and Invalid Input Detect Muting

- Selectable DDX® Ternary or Binary PWM output + Variable PWM Speeds

- Selectable De-emphasis

- Post-EQ User Programmable Mix with default 2.1 Bass Management settings

- Variable Max Power Correction for lower full-power THD

- Over-Current and Over-Temperature protection with programmable recovery

- Thermal-Warning Indicator with programmable auto output power reduction

- Four (4) Output Routing Configurations

- 24-bit, 96kHz Internal Processing

- BBE or BBE+Viva Processing\*

- \*Provided only under license from BBE Sound, Inc.

- QXpander\*\*

- \* \*Provided only under License of QSound Labs, Inc.

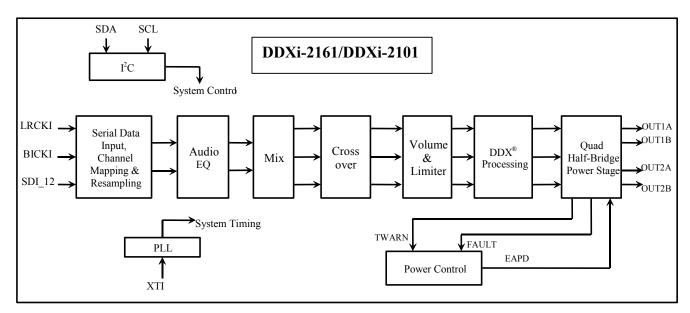

#### 1.0 GENERAL DESCRIPTION

The DDXi-2161 and DDXi-2101 (**DDXi-21x1**) are the world's first integrated solution including digital audio processing, digital amplifier control, and high-power output in a single DDX® chip delivering high-quality, high-efficiency, all digital amplification in a single compact package.

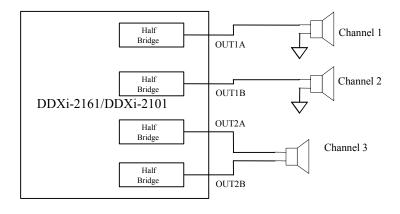

The DDXi-21x1 can be configured via digital control to operate in several output modes providing up to 2.1 channels of power output to speakers.

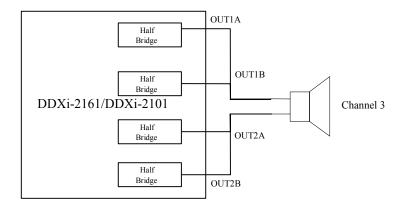

The DDXi-2161, in 2.1 mode, is capable of delivering up to:  $2 \times 35W + 1 \times 80W$ . In stereo mode it is capable of delivering up to:  $2 \times 80W$ . It can also be configured as a single bridge capable of high-current operation and delivering up to:  $1 \times 160W$ .

The DDXi-2101, in 2.1 mode, is capable of delivering up to:  $2 \times 30W + 1 \times 60W$ . In stereo mode it is capable of delivering up to:  $2 \times 60W$ . It can also be configured as a single bridge capable of high-current operation and delivering up to:  $1 \times 120W$ .

The DDXi-2161 and DDXi-2101 boast a full assortment of audio signal processing features that includes up to 4 programmable 24-bit biquads (EQ) per channel and bass/treble tone control. Automodes™ enable a time-to-market advantage by substantially reducing the amount of software development needed for certain functions. AutoMode settings include Auto Volume loudness control, preset volume curves, preset EQ settings, new advanced AM radio interference reduction modes, and more.

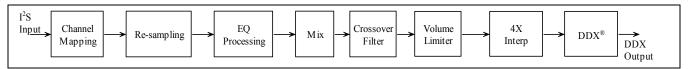

The serial audio data input interface accepts most formats, including the popular I<sup>2</sup>S format. Three channels of DDX<sup>®</sup> processing are provided. This high quality conversion from PCM audio to DDX's patented tri-state PWM switching waveform provides up to 99dB SNR and dynamic range.

# DDXi-2161 / DDXi-2101

# **Table of Contents**

| 1.0  | GENERAL DESCRIPTION                                          | 1        |

|------|--------------------------------------------------------------|----------|

| 1.1  | EQ Processing                                                | 5        |

| 1.2  | Mix Processing                                               |          |

| 1.3  | Output Mode Configurations                                   |          |

| 2.0  | PIN FUNCTION AND SPECIFICATIONS                              | 8        |

| 2.1  | Pin Description and Numbering                                | 8        |

| 2.2  | Absolute Maximum Ratings [Note 1]                            | <u>c</u> |

| 2.3  | Thermal Data                                                 |          |

| 2.4  | Electrical Characteristics.                                  | <u>S</u> |

| 2.5  | Operating Conditions                                         |          |

| 3.0  | FUNCTIONAL DESCRIPTION                                       | 12       |

| 3.1  | Pin Functional Description                                   | 12       |

| 3.2  | Pin Connection (Top View)                                    | 13       |

| 3.3  | Audio Performance                                            |          |

| 4.0  | I <sup>2</sup> C BUS SPECIFICATION                           | 18       |

| 4.1  | I <sup>2</sup> C Communication Protocol                      |          |

| 4.2  | Device Addressing                                            | 18       |

| 4.3  | Write Operation                                              |          |

| 4.4  | Read Operation                                               |          |

| 5.0  | REGISTER DESCRIPTION                                         | 20       |

| 5.1  | Configuration Register A (Address 00h)                       | 21       |

| 5.2  | Configuration Register B (Address 01h)                       |          |

| 5.3  | Configuration Register C (Address 02h)                       |          |

| 5.4  | Configuration Register D (Address 03h)                       |          |

| 5.5  | Configuration Register E (Address 04h)                       |          |

| 5.6  | Configuration Register F (Address 05h)                       |          |

| 5.7  | Volume and Mute Registers                                    |          |

| 5.8  | AutoMode Registers                                           |          |

| 5.9  | Channel Configuration Registers                              |          |

| 5.10 | \                                                            |          |

| 5.11 |                                                              |          |

| 6.0  | USER PROGRAMMABLE PROCESSING                                 |          |

| 6.1  | EQ – Biquad Equation                                         |          |

| 6.2  | Pre-Scale                                                    |          |

| 6.3  | Post-Scale                                                   |          |

| 6.4  | Mix/Bass Management                                          |          |

| 6.5  | Calculating 24-Bit Signed Fractional Numbers from a dB Value |          |

| 6.6  | User Defined Coefficient RAM                                 |          |

| 6.7  | Variable MAX Power Correction (Address 27h-28h):             |          |

| 6.8  | Fault Detect Recovery (Address 2Bh-2Ch):                     |          |

| 6.9  | Status Indicator Register (Address 2Dh)                      |          |

| 7.0  | DESIGN INFORMATION                                           |          |

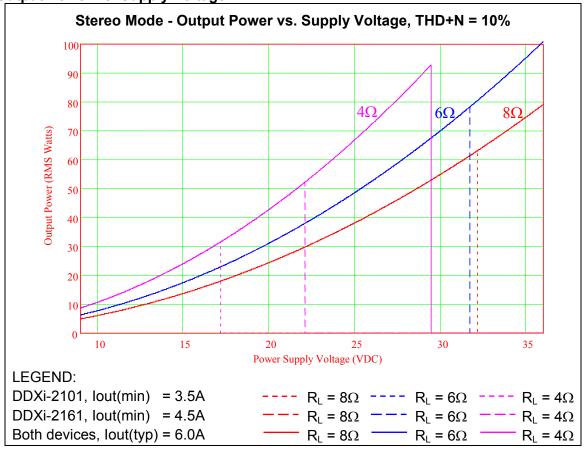

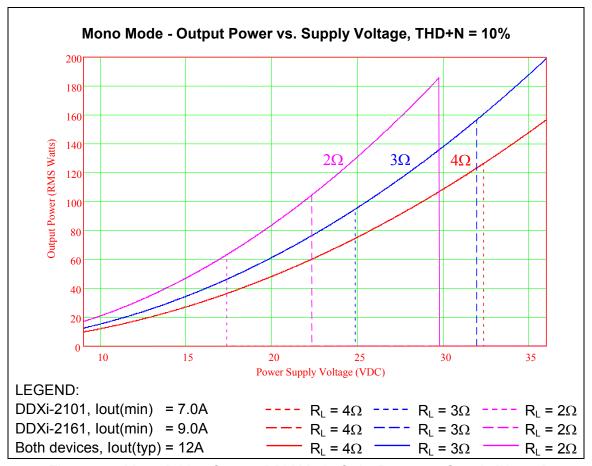

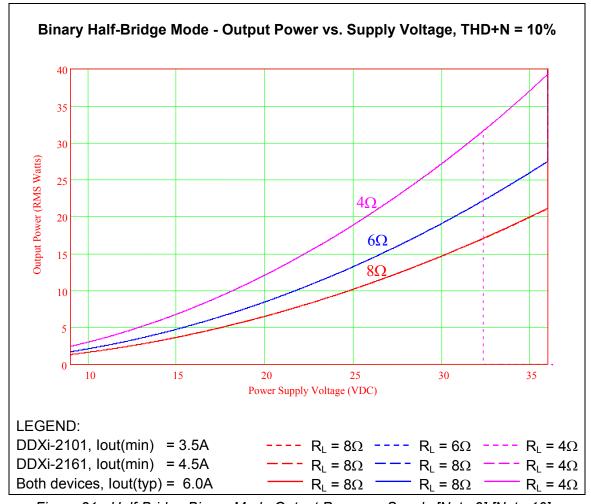

| 7.1  | Output Power vs. Supply Voltage                              |          |

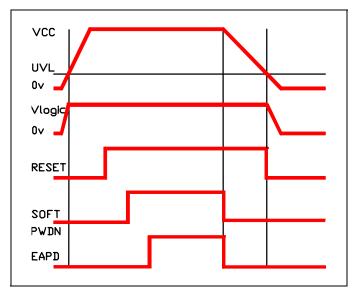

| 7.2  | Power Supply and Control Sequencing                          |          |

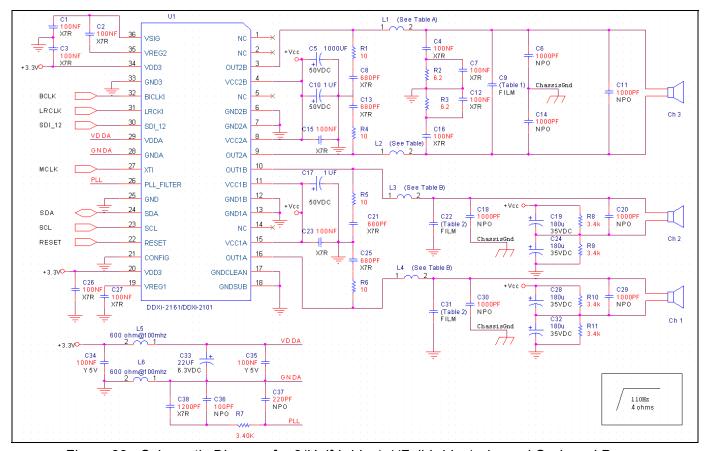

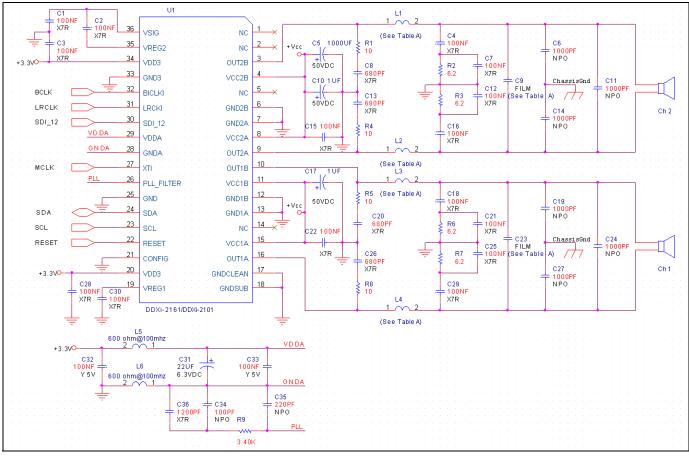

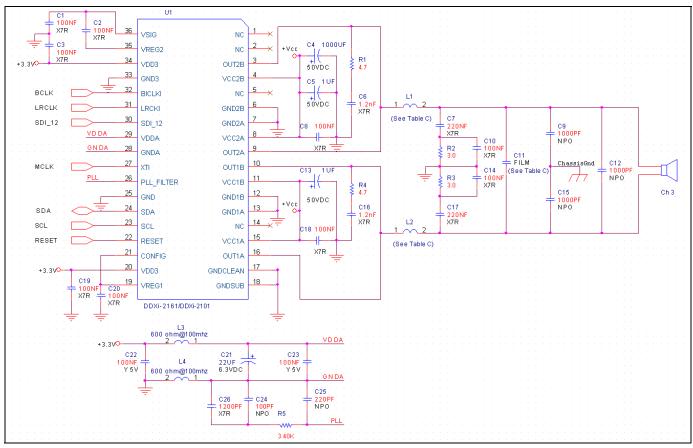

| 7.3  | Schematic Diagrams                                           |          |

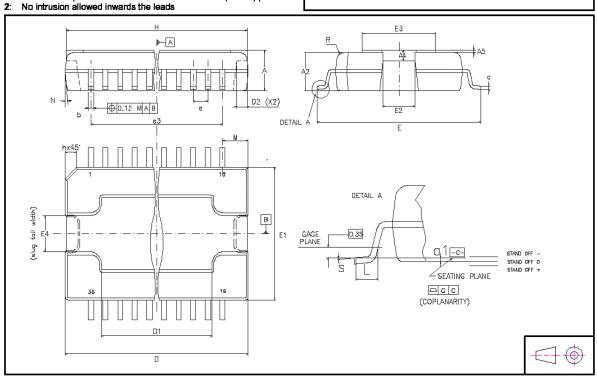

| 8.0  | Mechanical Drawing                                           |          |

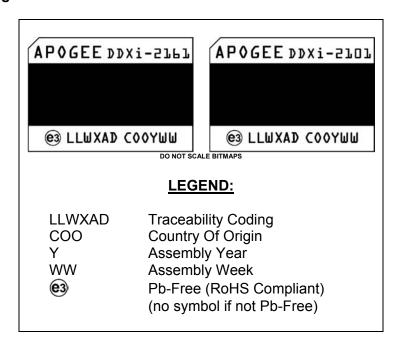

| 8.1  | Marking Configuration                                        | 58       |

# **Table of Figures**

| Figure 1 - Block Diagram                                                               | 5  |

|----------------------------------------------------------------------------------------|----|

| Figure 2 - Channel Signal Flow Diagram through the Digital Core                        | 5  |

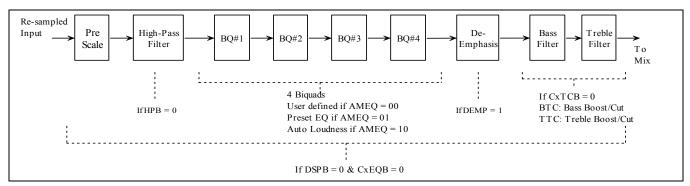

| Figure 3 - Channel Signal Flow through the EQ Block                                    | 5  |

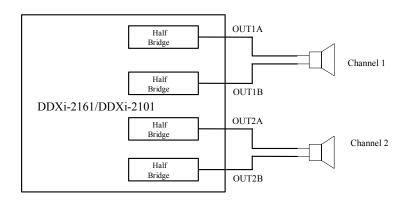

| Figure 4 - 2-Channel (Full-bridge) Power, OCFG(10) = 00                                | 6  |

| Figure 5 - 2.1-Channel Power Configuration OCFG(10) = 01                               | 6  |

| Figure 6 - Mono-Parallel Configuration, OCFG(10) = 11                                  | 7  |

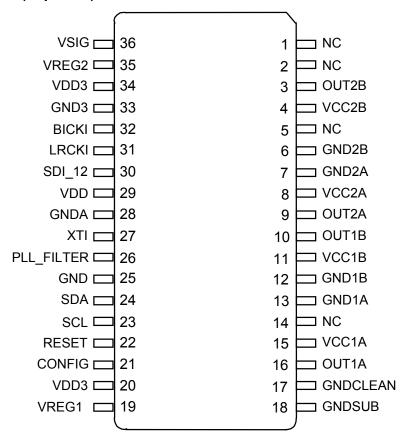

| Figure 7 - Pin Connection Diagram                                                      | 13 |

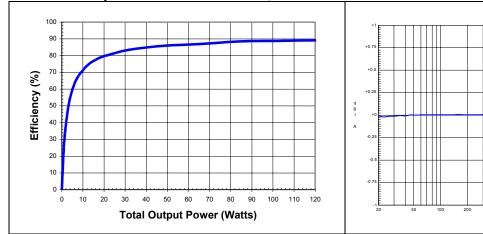

| Figure 8 - Typical Efficiency                                                          | 14 |

| Figure 9 - Typical Frequency Response                                                  | 14 |

| Figure 10 - FFT –60dB, 1kHz Output                                                     | 14 |

| Figure 11 - FFT Inter-Modulation Distortion 19kHz and 20kHz                            | 14 |

| Figure 12 - THD vs. Power, 1kHz                                                        | 15 |

| Figure 13 - THD vs. Frequency, 1W                                                      |    |

| Figure 14 - THD vs. Power, 1kHz                                                        | 15 |

| Figure 15 - THD vs. Frequency, 1W                                                      | 15 |

| Figure 16 - THD vs. Power, 1kHz                                                        | 16 |

| Figure 17 - THD vs. Frequency, 1W                                                      | 16 |

| Figure 18 - THD vs. Power, 1kHz                                                        |    |

| Figure 19 - THD vs. Frequency, 1W                                                      |    |

| Figure 20 - THD vs. Power, 1kHz                                                        |    |

| Figure 21 - THD vs. Frequency, 1W                                                      |    |

| Figure 22 - I <sup>2</sup> C Write Procedure                                           |    |

| Figure 23 - I <sup>2</sup> C Read Procedure                                            |    |

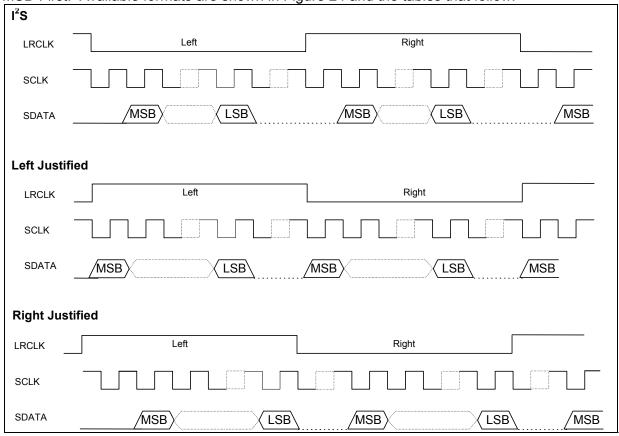

| Figure 24 - Serial Audio Input and Output Formats                                      |    |

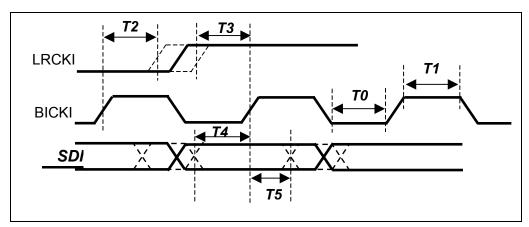

| Figure 25 - Serial Input Data Timing Characteristics                                   |    |

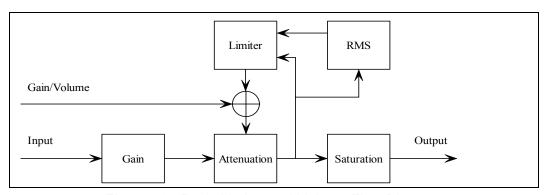

| Figure 26 - Basic Limiter and Volume Flow Diagram                                      |    |

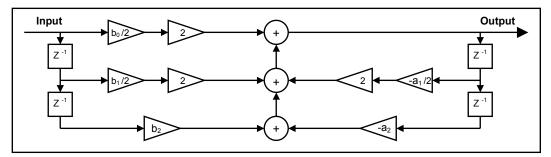

| Figure 27 - Biquad Filter Structure                                                    |    |

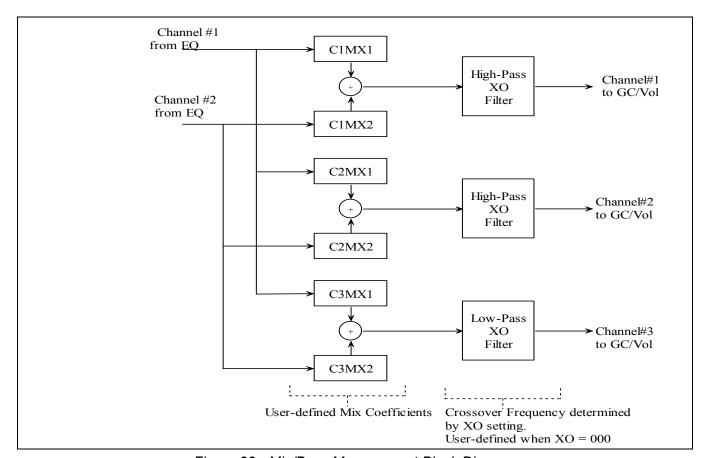

| Figure 28 - Mix/Bass Management Block Diagram                                          |    |

| Figure 29 - Output Power vs. Supply Voltage for Stereo Bridge                          |    |

| Figure 30 - Mono Bridge Output, DDX Mode Only, Power vs. Supply [Note 8]               |    |

| Figure 31 - Half-Bridge Binary Mode Output Power vs Supply [Note 9] [Note 10]          |    |

| Figure 32 – Recommended Power-Up & Power-Down Sequence                                 |    |

| Figure 33 - Schematic Diagram for 2(Half-bridge).1(Full-bridge)-channel On-board Power |    |

| Figure 34 - Schematic Diagram for 2-channel (Full-bridge) Power                        |    |

| Figure 35 - Schematic Diagram for 1-channel Mono-Parallel Power                        | 56 |

## **List of Tables**

| Table 1 - Pin Description and Numbering                                 | 8  |

|-------------------------------------------------------------------------|----|

| Table 2 - I <sup>2</sup> C Register Summary                             |    |

| Table 3 - IR and MCS Settings for Input Sample Rate and Clock Rate      | 21 |

| Table 4 - IR bit settings as a function of Input Sample Rate            |    |

| Table 5 - First Bit Selection Table                                     |    |

| Table 6 - Supported Serial Audio Input Formats                          | 24 |

| Table 7 - Serial Input Data Timing characteristics (Fs = 32 to 192kHz)  | 24 |

| Table 8 - DDX® Output Modes                                             |    |

| Table 9 - DDX® Compensating Pulse                                       | 26 |

| Table 10 - PWM Output Speed Selections                                  |    |

| Table 11 - Output Configuration Selections                              | 30 |

| Table 12 - Master Volume Offset as a function of MV (70)                | 32 |

| Table 13 - Channel Volume as a function of CxV (70)                     | 33 |

| Table 14 - AutoMode EQ                                                  | 34 |

| Table 15 - AutoMode Volume                                              |    |

| Table 16 - AutoMode Gain Compression/Limiters                           | 34 |

| Table 17 - AutoMode AM Switching Frequency Selection                    | 35 |

| Table 18 - Crossover Frequency Selection                                |    |

| Table 19 - Preset EQ Selection                                          |    |

| Table 20 - Channel Limiter Mapping Selection                            |    |

| Table 21 - Channel PWM Output Mapping                                   | 38 |

| Table 22 - Tone Control Boost/Cut Selection                             |    |

| Table 23 - Limiter Attack Rate Selection                                | 40 |

| Table 24 - Limiter Release Rate Selection                               |    |

| Table 25 - Limiter Attack Threshold Selection (AC-Mode)                 |    |

| Table 26 - Limiter Release Threshold Selection (AC-Mode).               |    |

| Table 27 - Limiter Attack Threshold Selection (DRC-Mode)                |    |

| Table 28 - Limiter Release Threshold Selection (DRC-Mode)               |    |

| Table 29 - RAM Block for Biquads, Mixing, and Scaling                   |    |

| Table 30 - Component Selection Table A for Full-Bridge Operation        |    |

| Table 31 - Component Selection Table B for Binary Half-Bridge Operation | 54 |

| Table 32 - Component Selection Table C for Mono Mode Operation          | 54 |

Figure 1 - Block Diagram

Figure 2 - Channel Signal Flow Diagram through the Digital Core

#### 1.1 EQ Processing

Two channels of re-sampled input data (96 kHz) are provided as input to the EQ processing block. Figure 3 below shows the internal signal flow through the EQ block. In this block, up to 4 user-defined Biquads can be applied to each of the two main processing channels. Pre-scaling, dc-blocking high-pass, de-emphasis, bass, and tone control filters can also be applied based on various configuration parameter settings. The entire EQ block can be bypassed for all channels simultaneously by setting the DSPB bit to '1'. The CxEQBP bits can be used to bypass the EQ block on a per channel basis.

Figure 3 - Channel Signal Flow through the EQ Block

This is preliminary information on a new product. Specifications are subject to change without notice.

## 1.2 Mix Processing

The Post-EQ Mix block takes the two channel outputs from the EQ block and outputs three channels of data. By default, Channels 1 and 2 outputs are essentially pass-through of Channels 1 and 2 inputs coming from the EQ block. An additional channel is created as a result of a sum & mix of the two input channels. See Figure 28. By default, this 3<sup>rd</sup> channel of data is an equal mix of channel 1 and 2 data. Normally this third channel will be used as the subwoofer in a 2.1 configuration. An additional filtering stage is found after the mix block in order to implement crossover filtering. The crossover filters can be automatically configured from the AutoMode Crossover (XO) bits or these filters can be manually programmed for any type and frequency crossover.

## 1.3 Output Mode Configurations

Figure 4 - 2-Channel (Full-bridge) Power, OCFG(1...0) = 00

Figure 5 - 2.1-Channel Power Configuration OCFG(1...0) = 01

Figure 6 - Mono-Parallel Configuration, OCFG(1...0) = 11

## 2.0 PIN FUNCTION AND SPECIFICATIONS

## 2.1 Pin Description and Numbering

Table 1 - Pin Description and Numbering

| Pin Name              | Pin No.      | Description                                                       |                                       |  |  |  |

|-----------------------|--------------|-------------------------------------------------------------------|---------------------------------------|--|--|--|

| Input and Clock Inter | face         |                                                                   |                                       |  |  |  |

| SCL                   | 23           | I <sup>2</sup> C Serial Clock, 5V Tolerant Schmitt                | Trig Input.                           |  |  |  |

| SDA                   | 24           | I <sup>2</sup> C Serial Data, bdir, 5V Tolerant Sch               | mitt Trig Input and 3.3V, 2mA Output. |  |  |  |

| XTI                   | 27           | PLL Clock, 5V Tolerant Input.                                     |                                       |  |  |  |

| SDI_12                | 30           | I <sup>2</sup> S Serial Data Channels 1 & 2, 5V To                | olerant Schmitt Trig Input.           |  |  |  |

| LRCKI                 | 31           | I <sup>2</sup> S Left/Right Frame Sync Clock, 5V Tolerant Input.  |                                       |  |  |  |

| BICKI                 | 32           | I <sup>2</sup> S Serial Bit Sync Clock, 5V Tolerant               | t Input.                              |  |  |  |

| Control/Miscellaneou  | IS           |                                                                   |                                       |  |  |  |

| CONFIG                | 21           | Logic Levels.                                                     |                                       |  |  |  |

| RESET                 | 22           | Reset (0=Reset, 1= Normal), 5V Tolerant Schmitt Trig Input.       |                                       |  |  |  |

| GND                   | 25           | Connect to ground.                                                |                                       |  |  |  |

| PLL_FILTER            | 26           | Connection to PLL Filter.  Refer to application schematic for PLI | L Filter details.                     |  |  |  |

| NC                    | 1,2,5,14     | Do not connect.                                                   |                                       |  |  |  |

| Power Outputs:        |              | DDX® Mode                                                         | Binary 2.1 Channel Mode               |  |  |  |

| OUT1A                 | 16           | Channel 1 Positive output.                                        | Channel 1 output.                     |  |  |  |

| OUT1B                 | 10           | Channel 1 Negative output.                                        | Channel 2 output.                     |  |  |  |

| OUT2A                 | 9            | Channel 2 Positive output.                                        | Channel 3 Positive output.            |  |  |  |

| OUT2B                 | 3            | Channel 2 Negative output.                                        | Channel 3 Negative output.            |  |  |  |

| Power Supplies        |              |                                                                   |                                       |  |  |  |

| VCC [2B, 2A, 1B, 1A]  | 4, 8, 11, 15 | Power Positive Supply                                             |                                       |  |  |  |

| GND [2B, 2A, 1B, 1A]  | 6, 7, 12, 13 | Power ground                                                      |                                       |  |  |  |

| GNDCLEAN              | 17           | Logic reference ground.                                           |                                       |  |  |  |

| GNDSUB                | 18           | Substrate ground.                                                 |                                       |  |  |  |

| VREG1                 | 19           | Internal +5V Regulator Voltage                                    |                                       |  |  |  |

| VDD3                  | 20           | Logic Supply to Power Section                                     |                                       |  |  |  |

| GNDA                  | 28           | PLL Analog Ground                                                 |                                       |  |  |  |

| VDDA                  | 29           | PLL Analog Supply (3.3V)                                          |                                       |  |  |  |

| GND3                  | 33           | Digital Ground                                                    |                                       |  |  |  |

| VDD3                  | 34           | Digital Power Supply Voltage (3.3V)                               |                                       |  |  |  |

| VREG2                 | 35           | Internal -5V (relative to VSIG) Regula                            | tor Voltage                           |  |  |  |

| VSIG                  | 36           | Signal Positive Supply                                            |                                       |  |  |  |

2.2 Absolute Maximum Ratings [Note 1]

| Symbol              | Parameter                                                      | Value               | Unit |

|---------------------|----------------------------------------------------------------|---------------------|------|

| V <sub>DD 3.3</sub> | 3.3V Digital Power Supply                                      | -0.5 to 4           | V    |

| $V_{DDA}$           | 3.3V Analog Power Supply                                       | -0.5 to 4           | V    |

| $V_{i}$             | Voltage on input pins                                          | -0.5 to (Vdd + 0.5) | V    |

| Vo                  | Voltage on output pins                                         | -0.5 to (Vdd + 0.5) | V    |

| V <sub>b</sub>      | Voltage on 5V tolerant inputs and bi-directional pins [Note 2] | -0.5 to 5.5         | V    |

| T <sub>stg</sub>    | Storage Temperature                                            | -40 to +150         | °C   |

| Tj                  | Operating Junction Temperature Range                           | 0 to +150           | °C   |

| $V_{CC}$            | Power supply voltage                                           | 40                  | V    |

| $V_L$               | Input logic reference                                          | 5.5                 | V    |

Note 1 - Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2 –Withstands -0.8V undershoot and 6.3V overshoots for 4ns max.

#### 2.3 Thermal Data

| SYMBOL            | PARAMETER                                            | MIN | TYP | MAX | UNIT |

|-------------------|------------------------------------------------------|-----|-----|-----|------|

| P <sub>TOT</sub>  | Power Dissipation, T <sub>heat-spreader</sub> = 25°C |     |     | 40  | W    |

| $\theta_{J-C}$    | Thermal resistance junction-case (heat spreader)     |     |     | 3.0 | °C/W |

| T <sub>j-SD</sub> | Thermal shut-down junction temperature               |     | 150 |     | °C   |

| T <sub>WARN</sub> | Thermal warning temperature                          |     | 130 |     | °C   |

| T <sub>hSD</sub>  | Thermal shut-down hysteresis                         |     | 25  |     | °C   |

#### 2.4 Electrical Characteristics.

(Unless otherwise noted,  $V_{CC} = 32V$ ,  $V_{DD3} = 3.3V$ ,  $T_c = 25^{\circ}C$ ,  $R_L = 8\Omega$ .)

| SYMBOL                                             | PARAMET                                     | ER                                     | CONDITION                                                                                        | MIN | TYP  | MAX | UNIT             |

|----------------------------------------------------|---------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------|-----|------|-----|------------------|

|                                                    |                                             |                                        | THD+N <10%, R <sub>L</sub> =3Ω, Vcc=33V                                                          | 160 |      |     |                  |

|                                                    | DDXi-2161 Power Per Channel                 | THD+N <1%, $R_L$ =3 $\Omega$ , Vcc=33V | 125                                                                                              |     |      |     |                  |

| P <sub>O-DM</sub> (DDX <sup>®</sup>                | DDXI-2101 FOWEI FE                          | Chamile                                | THD+N <10%, R <sub>L</sub> =4Ω, Vcc=36V                                                          |     | 150  |     | W <sub>RMS</sub> |

| Mono Mode)                                         |                                             |                                        | THD+N <1%, $R_L$ =4 $\Omega$ , Vcc=36V                                                           |     | 115  |     | VVRMS            |

|                                                    | DDXi-2101 Power Pe                          | r Channol                              | THD+N <10%, R <sub>L</sub> =4Ω, Vcc=32V                                                          | 120 |      |     |                  |

|                                                    | DDXI-21011 OWELLE                           | Chamilei                               | THD+N <1%, $R_L$ =4 $\Omega$ , Vcc=32V                                                           | 93  |      |     |                  |

|                                                    |                                             |                                        | THD+N <10%, R <sub>L</sub> =6Ω, Vcc=33V                                                          | 80  |      |     |                  |

| D (DDV®                                            | DDXi-2161 Power Pe                          | r Channel                              | THD+N <1%, $R_L$ =6 $\Omega$ , Vcc=33V                                                           | 62  |      |     |                  |

| P <sub>O-DF</sub> (DDX <sup>®</sup><br>Full Bridge | DDXI-21011 OWELLE                           | Chamilei                               | THD+N <10%, $R_L$ =8 $\Omega$ , Vcc=36V                                                          |     | 75   |     | W <sub>RMS</sub> |

| Mode)                                              |                                             |                                        | THD+N <1%, R <sub>L</sub> =8Ω, Vcc=36V                                                           |     | 58   |     | VVRMS            |

| (Wode)                                             | DDXi-2101 Power Per Channel                 |                                        | THD+N <10%, R <sub>L</sub> =8Ω, Vcc=32V                                                          | 60  |      |     |                  |

|                                                    | DDXI-2 IUT FUWEI FE                         | Charine                                | THD+N <1%, R <sub>L</sub> =8Ω, Vcc=32V                                                           | 48  |      |     |                  |

|                                                    |                                             | 2 x Half                               | THD+N <10%, R <sub>L</sub> =4Ω, Vcc=33V                                                          | 30  |      |     |                  |

| _                                                  | DDXi-2161 Power Bridge Per Channel 2 x Half | Bridge                                 | THD+N <1%, $R_L$ =4 $\Omega$ , Vcc=33V                                                           | 24  |      |     |                  |

| P <sub>O-Bin</sub><br>(2.1 Channel                 |                                             | 2 x Half                               | THD+N <10%, R <sub>L</sub> =4Ω, Vcc=36V                                                          |     | 40   |     | W <sub>RMS</sub> |

| Mode)                                              |                                             | Bridge                                 | THD+N <1%, $R_L$ =4 $\Omega$ , Vcc=36V                                                           |     | 30   |     | VVRMS            |

| Wiode)                                             | DDXi-2101 Power                             | 2 x Half                               | THD+N <10%, $R_L$ =4 $\Omega$ , Vcc=32V                                                          | 30  |      |     |                  |

|                                                    | Per Channel                                 | Bridge                                 | THD+N <1%, $R_L$ =4 $\Omega$ , Vcc=32V                                                           | 23  |      |     |                  |

|                                                    | Total Harmonic                              | DDXi-2161                              | Po=1 Wrms, Vcc=33V, R <sub>L</sub> =6Ω                                                           |     | 0.09 |     | %                |

| THD+N                                              | Distortion + Noise                          | (DDX Mode)                             | Po=32 Wrms, Vcc=33V, R <sub>L</sub> =6Ω                                                          |     | 0.10 |     | 70               |

| ITIDIN                                             | Total Harmonic                              | DDXi-2101                              | Po=1 Wrms, Vcc=32V, R <sub>L</sub> =8Ω                                                           |     | 0.09 |     | %                |

|                                                    | Distortion + Noise                          | (DDX Mode)                             | Po=25 Wrms, Vcc=32V, $R_L$ =8 $\Omega$                                                           |     | 0.08 |     | 70               |

| CNID                                               | Signal to Noise Ratio,                      | DDX <sup>®</sup> Mode                  | A-Weighted (NSBW = 1)                                                                            |     | 100  |     | 4D               |

| SNR                                                | Signal to Noise Ratio,                      | Binary Mode                            | A-Weighted (NSBW = 1)                                                                            |     | 90   |     | dB               |

| PSRR                                               | Power Supply Rejection                      | on Ratio                               | Stereo DDX Mode, < 5 kHz<br>V <sub>RIPPLE</sub> =1 V <sub>RMS</sub><br>Audio Input = Dither Only |     | 80   |     | dB               |

#### 2.4 Electrical Characteristics.

(Unless otherwise noted,  $V_{CC}$  = 32V,  $V_{DD3}$  = 3.3V,  $T_c$  = 25°C,  $R_L$  = 8 $\Omega$ .)

| SYMBOL             | PARAMETER                                       | CONDITION                                                                      | MIN | TYP | MAX | UNIT |

|--------------------|-------------------------------------------------|--------------------------------------------------------------------------------|-----|-----|-----|------|

| X <sub>TALK</sub>  | Crosstalk                                       | Stereo DDX Mode, < 5 kHz<br>One Channel Driven @ 1 W<br>Other Channel Measured |     | 80  |     | dB   |

|                    | Peak Efficiency, DDX® Mode                      | Po=2 x 50 W, 8Ω                                                                |     | 89  |     | %    |

| η                  | Peak Efficiency, Binary Mode                    | Po=2 x 25 W, $4\Omega$ + 1 x 50W, $8\Omega$                                    |     | 87  |     | 70   |

| 1                  | Speaker Output Short-Circuit                    | DDXi-2161                                                                      | 4.5 | 6   | 8   | ۸    |

| SC                 | Protection Limit per Bridge                     | DDXi-2101                                                                      | 3.5 | 0   | 0   | Α    |

| R <sub>ds-on</sub> | Power MOSFET output resistance                  | I <sub>d</sub> =1A                                                             |     | 200 | 270 | mΩ   |

| gи                 | Power Nchannel R <sub>ds-on</sub> matching      | I <sub>d</sub> = 1A                                                            | 95  |     |     | %    |

| I <sub>dss</sub>   | Power Pchannel/Nchannel leakage                 | $V_{CC} = 35 \text{ V}$                                                        |     |     | 50  | uA   |

| UVL                | Under-voltage Lockout Threshold                 |                                                                                |     | 7   | 9   | V    |

| <b>I</b> PD        | V <sub>CC</sub> supply current, Power-down      | Soft-Pwdn or EAPD = 0                                                          |     | <1  |     | mA   |

| 1                  | 2-channel mode V <sub>CC</sub> supply current   | 2-Channel switching at 384kHz                                                  |     | 94  |     | mA   |

| Icc                | 2.1-channel mode V <sub>CC</sub> supply current | 2.1-Channel switching at 384kHz                                                |     | 108 |     | IIIA |

| t <sub>r</sub>     | Rise time                                       | Resistive load                                                                 | •   |     | 25  | ns   |

| t <sub>f</sub>     | Fall Time                                       | Resistive load                                                                 |     |     | 25  | ns   |

## 2.5 Operating Conditions

2.5.1 Recommended DC Operating Conditions [Note 3]

| SYMBOL          | PARAMETER                         | MIN | TYP | MAX | UNIT |

|-----------------|-----------------------------------|-----|-----|-----|------|

| V <sub>CC</sub> | Power supply voltage              | 9   |     | 36  | V    |

| $V_{DD3}$       | 3.3V Digital Power Supply Voltage | 3.0 |     | 3.6 | V    |

| $V_{DDA}$       | 3.3V Analog Power Supply          | 3.0 |     | 3.6 | V    |

| T <sub>A</sub>  | Operating Ambient Temperature     | 0   |     | 70  | °C   |

Note 3 - Performance not guaranteed beyond recommended operating conditions.

2.5.2 DC Electrical Characteristics: 5V Tolerant Input Buffers

| SYMBOL              | PARAMETER                  | CONDITION             | MIN. | TYP. | MAX. | UNIT |

|---------------------|----------------------------|-----------------------|------|------|------|------|

| $V_{IL}$            | Low Level Input Voltage    |                       |      |      | 8.0  | V    |

| $V_{IH}$            | High Level Input Voltage   |                       | 2.0  |      |      | V    |

| $V_{ILhyst}$        | Low Level Threshold        | Input Falling         | 8.0  |      | 1.35 | V    |

| V <sub>IHhyst</sub> | High Level Threshold       | Input Rising          | 1.3  |      | 2.0  |      |

| V <sub>hyst</sub>   | Schmitt Trigger Hysteresis |                       | 0.3  |      | 8.0  | V    |

| I <sub>IL</sub>     | Low Level Input Current    | Vi = 0V [Note 4]      | 40   | 60   | 110  | uA   |

| I <sub>IH</sub>     | High Level Input Current   | Vi = VDD_3.3 [Note 4] | 25   | 60   | 110  | uA   |

Note 4 - Min condition: Vdd=3V, 125°C; Max condition: Vdd=3.6V, -40°C.

2.5.3 Operating Characteristics

| SYMBOL            | PARAMETER                  | CONDITION              | MIN. | TYP. | MAX. | UNIT |

|-------------------|----------------------------|------------------------|------|------|------|------|

|                   | Operating Current 3.3V     | All channels operating |      | 6    | 8    | mA   |

| I <sub>VDD</sub>  | PowerDown Current 3.3V     | PowerDown Asserted     |      | 2    | 3    | mA   |

| 1                 | PLL Operating Current 3.3V |                        |      | 9    | 12   | MA   |

| I <sub>VDDA</sub> | PLL PowerDown Current 3.3V | PowerDown Asserted     |      | 2    | 3    | mA   |

## 2.5.4 Electrical Characteristics

$(V_{DD3}=3.3\pm0.3V, TA=0 \text{ to } 70^{\circ}\text{C unless otherwise specified})$

| SYMBOL    | PARAMETER                | CONDITION             | MIN. | TYP. | MAX. | UNIT |

|-----------|--------------------------|-----------------------|------|------|------|------|

| $V_{ESD}$ | Electrostatic Protection | Leakage <1uA (Note 5) | 2000 |      |      | V    |

Note 5 - Human Body Model.

## 2.5.5 Timing Characteristics

$(V_{DD3} = 3.3 \pm 0.3 \text{V}, T_A = 0 \text{ to } 70^{\circ}\text{C} \text{ unless otherwise specified})$

| SYMBOL             | PARAMETER              | TEST CONDITION            | MIN. | TYP. | MAX. | UNIT |

|--------------------|------------------------|---------------------------|------|------|------|------|

| t <sub>reset</sub> | Reset hold time        | Active Low Reset (pin 15) | 100  |      |      | nSec |

| VCO<br>Free_Run    | VCO Free Run Frequency | No Clock applied to XTI   | 18   | 28   |      | MHz  |

Note 6 - The DDXi-2161 and DDXi-2101 are designed to operate at a minimum free-run frequency when there is no clock applied at XTI. This assures proper  $l^2C$  communication without a valid master clock. The device is not designed to process audio data without a valid clock applied at XTI.

#### 3.0 FUNCTIONAL DESCRIPTION

## 3.1 Pin Functional Description

## 3.1.1 OUT1A, 1B, 2A & 2B (Pins 16, 10, 9 & 3)

Half Bridge Power Outputs 1A, 1B, 2A & 2B deliver audio power to the speaker loads. Using DDX stereo configuration mode, outputs 1A (+) and 1B (-) comprise Channel 1 and outputs 2A (+) and 2B (-) comprise Channel 2. Using binary 2.1 channel configuration mode, output 1A is for Channel 1 and output 1B is for Channel 2 and outputs 2A (+) and 2B (-) comprise Channel 3. Using DDX mono-high power output mode (Config connected to VREG1), outputs 1A and 1B are shorted (+) and outputs 2A and 2B are shorted (-) comprising a single BTL output with double the output current capability for Channel 3. Operation as four individual half-bridges is not supported.

#### 3.1.2 **RESET (Pin 22)**

Driving RESET low sets all outputs low and returns all register settings to their defaults. The reset is asynchronous to the internal clock.

## 3.1.3 I<sup>2</sup>C Signals (Pins 23 & 24)

The SDA ( $I^2C$  Serial Data) and SCL ( $I^2C$  Serial Clock) pins operate per the  $I^2C$  specification. See Section 4.0. Fast-mode (400kB/sec)  $I^2C$  communication is supported.

#### 3.1.4 GNDA & VDDA: Phase Locked Loop Power (Pins 28-29)

The phase locked loop power is applied here. This +3.3V supply must be well bypassed and filtered for noise immunity. The audio performance of the device is critically dependent upon the PLL circuit. Refer to application schematics for suggested filtering.

## 3.1.5 XTI: PLL Clock In (Pin 27)

The master clock applied on this pin for the PLL is required for the operation of the digital core. The master clock must be an integer multiple of the LR clock frequency. Typically, the master clock frequency is 12.288 MHz (256\*Fs) for a 48kHz sample rate, which is the default at power-up. Care must be taken to avoid over-clocking the device, i.e provide the device with the nominally required system clock; otherwise, the device may not properly operate or be able to communicate.

#### 3.1.6 PLL FILTER: PLL Filter (Pin 26)

This pin connects to external filter components for PLL loop compensation. Refer to the application schematics for the recommended PLL loop compensation circuit.

#### 3.1.7 BICKI: I<sup>2</sup>S Serial Clock In (Pin 32)

The serial or bit clock input is used for framing each data bit. The bit clock frequency is typically 64\*Fs, for example, using I<sup>2</sup>S serial format.

## 3.1.8 SDI\_12: I<sup>2</sup>S Serial Data Input (Pin 30)

PCM audio information enters the device here. Six format choices are available including I<sup>2</sup>S, left- or right-justified, LSB or MSB first, with word widths of 16, 18, 20, and 24 bits.

#### 3.1.9 LRCKI: I<sup>2</sup>S Left/Right Clock In (Pin 31)

The Left/Right clock input is used for data word framing. The clock frequency will be at the input sample rate Fs.

#### 3.1.10 CONFIG: Configuration input (Pin 21)

The configuration input pin is normally connected to ground. Using the mono-high power BTL configuration requires the CONFIG input pin be shorted to VREG1.

## 3.1.11 VREG1: Internal regulator bypass (Pin 19)

Connect a 100nF bypass capacitor to this pin to stabilize the internal +5V regulator in the power stage.

## 3.1.12 VREG2: Internal regulator bypass (Pin 35)

Connect a 100nF bypass capacitor between this pin and VSIG to stabilize the internal -5V regulator in the power stage. Note, VREG2 is measured relative to VSIG.

## 3.1.13 VSIG: Signal Positive Supply (Pin 36)

Connect a 100nF bypass capacitor to this pin to stabilize the reference for the upper regulator in the power stage.

#### 3.1.14 GNDSUB: Substrate ground (Pin 18)

Connect this pin to power ground plane.

## 3.1.15 GNDCLEAN: Clean ground (Pin19)

This pin is the logic ground reference for the power section. Connect this pin to digital ground plane. Note, digital and power ground planes must be combined under the IC.

# 3.1.16 VCC1A,1B,2A,2B and GND1A,1B,2A,2B: Bridge Power Supply (Pins 15,11,8,4 and Pins 13,12,7,6)

These pins supply voltage to the power stage section using one power pair for each half bridge. It is absolutely critical to bypass well using low-inductance PCB routing for these power inputs. Apogee provides reference circuit/PCB designs to adopt for customer applications. It is strongly recommended to obtain these designs from application support and copy the application circuit/layout exactly.

## 3.1.17 VDD3 and GND3: Digital power supply (Pins 20,34 and 33).

Connect 100nF bypass capacitors very close to these supply pins.

## 3.2 Pin Connection (Top View)

Figure 7 - Pin Connection Diagram.

#### 3.3 Audio Performance

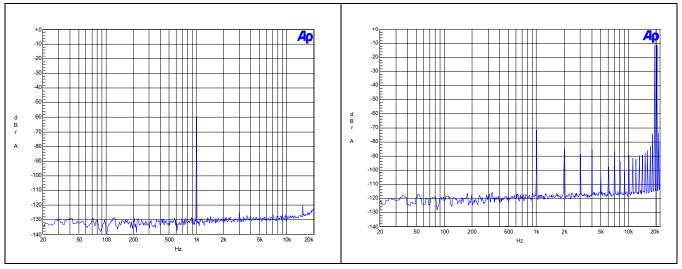

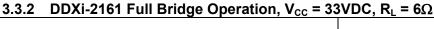

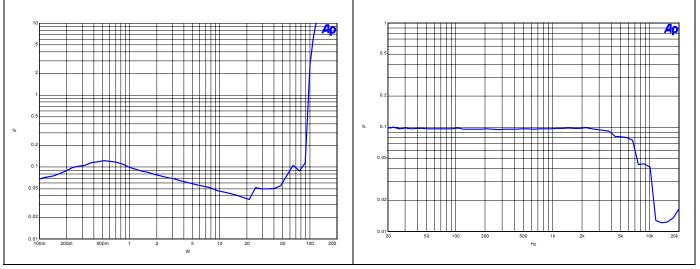

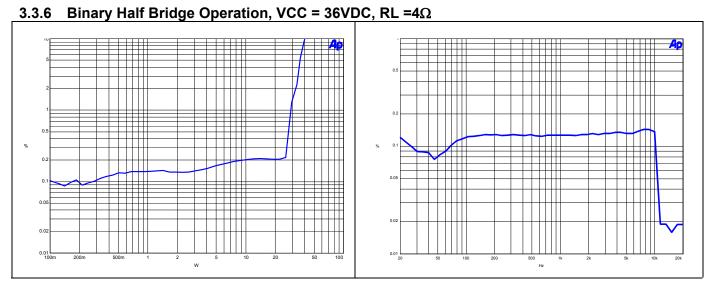

3.3.1 DDX Operation with Vcc = 32V, 8 Ohm load

Figure 8 - Typical Efficiency

Figure 9 - Typical Frequency Response

Figure 10 - FFT -60dB, 1kHz Output

Figure 11 - FFT Inter-Modulation Distortion 19kHz and 20kHz

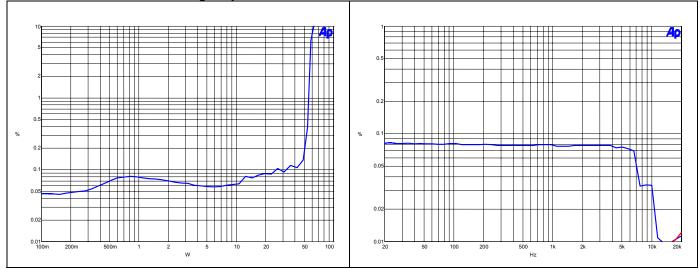

Figure 12 - THD vs. Power, 1kHz

Figure 13 - THD vs. Frequency, 1W

Figure 14 - THD vs. Power, 1kHz

Figure 15 - THD vs. Frequency, 1W

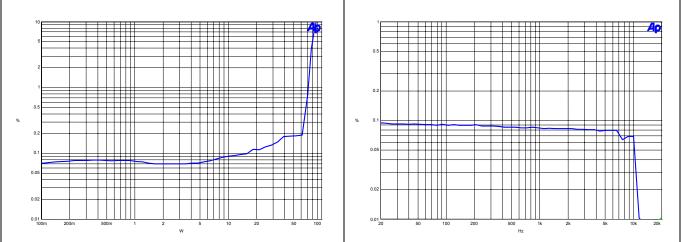

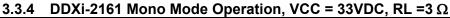

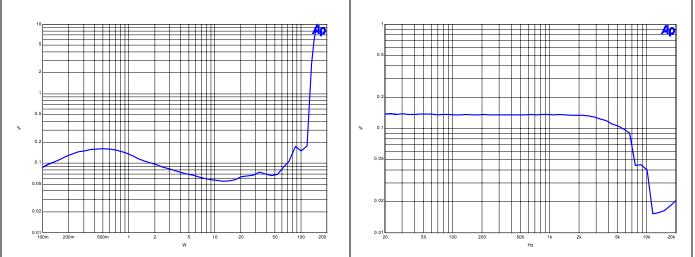

Figure 16 - THD vs. Power, 1kHz

Figure 17 - THD vs. Frequency, 1W

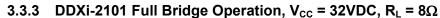

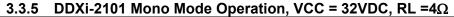

Figure 18 - THD vs. Power, 1kHz

Figure 19 - THD vs. Frequency, 1W

Figure 20 - THD vs. Power, 1kHz

Figure 21 - THD vs. Frequency, 1W

### 4.0 I2C BUS SPECIFICATION

The DDXi-2161 and DDXi-2101 (**DDXi-21x1**) support the I<sup>2</sup>C fast mode protocol (400 kb/sec). This protocol defines any device that sends data on to the bus as a transmitter and any device that reads the data as a receiver. The device that controls the data transfer is known as the master and the other as the slave. The master always starts the transfer and provides the serial clock for synchronization. The DDXi-21x1 is always a slave device in all of its communications.

## 4.1 I<sup>2</sup>C Communication Protocol

## 4.1.1 Data Transition or change

Data changes on the SDA line must only occur when the SCL clock is low. SDA transition while the clock is high is used to identify a START or STOP condition.

#### 4.1.2 Start Condition

START is identified by a high to low transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A START condition must precede any command for data transfer.

## 4.1.3 Stop Condition

STOP is identified by a low to high transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A STOP condition terminates communication between the DDXi-21x1 and the bus master.

## 4.1.4 Data Input

During the data input the DDXi-21x1 samples the SDA signal on the rising edge of clock SCL. For correct device operation the SDA signal must be stable during the rising edge of the clock and the data can change only when the SCL line is low.

## 4.2 Device Addressing

To start communication between the master and the DDXi-21x1, the master must initiate with a start condition. Following this, the master sends 8-bits (MSB first) onto the SDA line corresponding to the device select address and read or write mode.

The 7 most significant bits are the device address identifiers, corresponding to the  $I^2C$  bus definition. In the DDXi-21x1 the  $I^2C$  interface uses a device address of 0x34 or 0011010x.

The 8th bit (LSB) identifies read or write operation, RW. This bit is set to 1 in read mode and 0 for write mode. After a START condition the DDXi-21x1 identifies the device address on the bus. If a match is found, it acknowledges the identification on the SDA bus during the 9th bit time. The byte following the device identification byte is the internal space address.

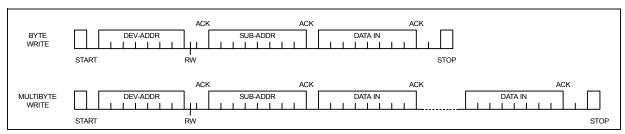

#### 4.3 Write Operation

Following the START condition the master sends a device select code with the RW bit set to 0. The DDXi-21x1 acknowledges this and then the master writes the internal address byte. After receiving the internal byte address the DDXi-21x1 again responds with an acknowledgement.

#### 4.3.1 Byte Write

In the byte write mode the master sends one data byte. This is acknowledged by the DDXi-21x1. The master then terminates the transfer by generating a STOP condition.

#### 4.3.2 Multi-byte Write

The multi-byte write modes can start from any internal address. Sequential data byte writes will be written to sequential addresses within the DDXi-21x1. The master generating a STOP condition terminates the transfer.

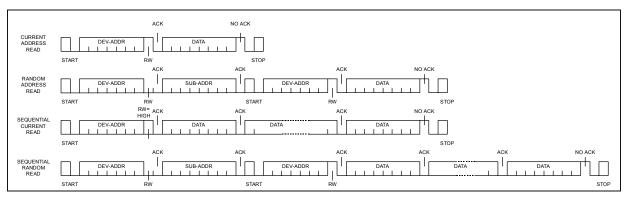

#### 4.4 Read Operation

## 4.4.1 Current Address Byte Read

Following the START condition the master sends a device select code with the RW bit set to 1. The DDXi-21x1 acknowledges this and then responds by sending one byte of data. The master then terminates the transfer by generating a STOP condition.

## 4.4.1.1 Current Address Multi-byte Read

The multi-byte read modes can start from any internal address. Sequential data bytes will be read from sequential addresses within the DDXi-21x1. The master acknowledges each data byte read and then generates a STOP condition terminating the transfer.

## 4.4.2 Random Address Byte Read

Following the START condition the master sends a device select code with the RW bit set to 0. The DDXi-21x1 acknowledges this and then the master writes the internal address byte. After receiving, the internal byte address the DDXi-21x1 again responds with an acknowledgement. The master then initiates another START condition and sends the device select code with the RW bit set to 1. The DDXi-2101 acknowledges this and then responds by sending one byte of data. The master then terminates the transfer by generating a STOP condition.

## 4.4.2.1 Random Address Multi-byte Read

The multi-byte read modes could start from any internal address. Sequential data bytes will be read from sequential addresses within the DDXi-21x1. The master acknowledges each data byte read and then generates a STOP condition terminating the transfer.

## Write Mode Sequence

Figure 22 - I<sup>2</sup>C Write Procedure

## **Read Mode Sequence**

Figure 23 - I<sup>2</sup>C Read Procedure

## 5.0 REGISTER DESCRIPTION

Table 2 - I<sup>2</sup>C Register Summary

| Address | Name    | D7     | D6     | D5     | D4     | D3     | D2     | D1     | D0    |

|---------|---------|--------|--------|--------|--------|--------|--------|--------|-------|

| 0x00    | ConfA   | FDRB   | TWAB   | TWRB   | IR1    | IR0    | MCS2   | MCS1   | MCS0  |

| 0x01    | ConfB   | C2IM   | C1IM   | DSCKE  | SAIFB  | SAI3   | SAI2   | SAI1   | SAI0  |

| 0x02    | ConfC   |        | CSZ4   | CSZ3   | CSZ2   | CSZ1   | CSZ0   | OM1    | OM0   |

| 0x03    | ConfD   | MME    | ZDE    | DRC    | BQL    | PSL    | DSPB   | DEMP   | HPB   |

| 0x04    | ConfE   | SVE    | ZCE    | DCCV   | PWMS   | AME    | NSBW   | MPC    | MPCV  |

| 0x05    | ConfF   | EAPD   | PWDN   | ECLE   | LDTE   | BCLE   | IDE    | OCFG1  | OCFG0 |

| 0x06    | Mmute   |        |        |        |        | C3M    | C2M    | C1M    | MMute |

| 0x07    | Mvol    | MV7    | MV6    | MV5    | MV4    | MV3    | MV2    | MV1    | MV0   |

| 0x08    | C1Vol   | C1V7   | C1V6   | C1V5   | C1V4   | C1V3   | C1V2   | C1V1   | C1V0  |

| 0x09    | C2Vol   | C2V7   | C2V6   | C2V5   | C2V4   | C2V3   | C2V2   | C2V1   | C2V0  |

| 0x0A    | C3Vol   | C3V7   | C3V6   | C3V5   | C3V4   | C3V3   | C3V2   | C3V1   | C3V0  |

| 0x0B    | Auto1   | AMPS   |        | AMGC1  | AMGC0  | AMV1   | AMV0   | AMEQ1  | AMEQ0 |

| 0x0C    | Auto2   | XO3    | XO2    | XO1    | XO0    | AMAM2  | AMAM1  | AMAM0  | AMAME |

| 0x0D    | Auto3   |        |        |        | PEQ4   | PEQ3   | PEQ2   | PEQ1   | PEQ0  |

| 0x0E    | C1Cfg   | C1OM1  | C1OM0  | C1LS1  | C1LS0  | C1BO   | C1VBP  | C1EQBP | C1TCB |

| 0x1F    | C2Cfg   | C2OM1  | C2OM0  | C2LS1  | C2LS0  | C2BO   | C2VBP  | C2EQBP | C2TCB |

| 0x10    | C3Cfg   | C3OM1  | C3OM0  | C3LS1  | C3LS0  | C3BO   | C3VBP  |        |       |

| 0x11    | Tone    | TTC3   | TTC2   | TTC1   | TTC0   | BTC3   | BTC2   | BTC1   | BTC0  |

| 0x12    | L1ar    | L1A3   | L1A2   | L1A1   | L1A0   | L1R3   | L1R2   | L1R1   | L1R0  |

| 0x13    | L1atrt  | L1AT3  | L1AT2  | L1AT1  | L1AT0  | L1RT3  | L1RT2  | L1RT1  | L1RT0 |

| 0x14    | L2ar    | L2A3   | L2A2   | L2A1   | L2A0   | L2R3   | L2R2   | L2R1   | L2R0  |

| 0x15    | L2atrt  | L2AT3  | L2AT2  | L2AT1  | L2AT0  | L2RT3  | L2RT2  | L2RT1  | L2RT0 |

| 0x16    | Cfaddr2 | CFA7   | CFA6   | CFA5   | CFA4   | CFA3   | CFA2   | CFA1   | CFA0  |

| 0x17    | B1cf1   | C1B23  | C1B22  | C1B21  | C1B20  | C1B19  | C1B18  | C1B17  | C1B16 |

| 0x18    | B1cf2   | C1B15  | C1B14  | C1B13  | C1B12  | C1B11  | C1B10  | C1B9   | C1B8  |

| 0x19    | B1cf3   | C1B7   | C1B6   | C1B5   | C1B4   | C1B3   | C1B2   | C1B1   | C1B0  |

| 0x1A    | B2cf1   | C2B23  | C2B22  | C2B21  | C2B20  | C2B19  | C2B18  | C2B17  | C2B16 |

| 0x1B    | B2cf2   | C2B15  | C2B14  | C2B13  | C2B12  | C2B11  | C2B10  | C2B9   | C2B8  |

| 0x1C    | B2cf3   | C2B7   | C2B6   | C2B5   | C2B4   | C2B3   | C2B2   | C2B1   | C2B0  |

| 0x1D    | A1cf1   | C3B23  | C3B22  | C3B21  | C3B20  | C3B19  | C3B18  | C3B17  | C3B16 |

| 0x1E    | A1cf2   | C3B15  | C3B14  | C3B13  | C3B12  | C3B11  | C3B10  | C3B9   | C3B8  |

| 0x1F    | A1cf3   | C3B7   | C3B6   | C3B5   | C3B4   | C3B3   | C3B2   | C3B1   | C3B0  |

| 0x20    | A2cf1   | C4B23  | C4B22  | C4B21  | C4B20  | C4B19  | C4B18  | C4B17  | C4B16 |

| 0x21    | A2cf2   | C4B15  | C4B14  | C4B13  | C4B12  | C4B11  | C4B10  | C4B9   | C4B8  |

| 0x22    | A2cf3   | C4B7   | C4B6   | C4B5   | C4B4   | C4B3   | C4B2   | C4B1   | C4B0  |

| 0x23    | B0cf1   | C5B23  | C5B22  | C5B21  | C5B20  | C5B19  | C5B18  | C5B17  | C5B16 |

| 0x24    | B0cf2   | C5B15  | C5B14  | C5B13  | C5B12  | C5B11  | C5B10  | C5B9   | C5B8  |

| 0x25    | B0cf3   | C5B7   | C5B6   | C5B5   | C5B4   | C5B3   | C5B2   | C5B1   | C5B0  |

| 0x26    | Cfud    |        |        |        |        | RA     | R1     | WA     | W1    |

| 0x27    | MPCC1   | MPCC15 | MPCC14 | MPCC13 | MPCC12 | MPCC11 | MPCC10 | MPCC9  | MPCC8 |

| 0x28    | MPCC2   | MPCC7  | MPCC6  | MPCC5  | MPCC4  | MPCC3  | MPCC2  | MPCC1  | MPCC0 |

| 0x29    | RES     | RES    | RES    | RES    | RES    | RES    | RES    | RES    | RES   |

| 0x2A    | RES     | RES    | RES    | RES    | RES    | RES    | RES    | RES    | RES   |

| 0x2B    | FDRC1   | FDRC15 | FDRC14 | FDRC13 | FDRC12 | FDRC11 | FDRC10 | FDRC9  | FDRC8 |

| 0x2C    | FDRC2   | FDRC7  | FDRC6  | FDRC5  | FDRC4  | FDRC3  | FDRC2  | FDRC1  | FDRC0 |

| 0x2D    | Status  | PLLUL  |        |        |        |        |        | FAULT  | TWARN |

5.1 Configuration Register A (Address 00h)

| <u> </u> | or comigaration regiotor it preadless to |      |     |     |      |      |      |  |  |  |

|----------|------------------------------------------|------|-----|-----|------|------|------|--|--|--|

| D7       | D6                                       | D5   | D4  | D3  | D2   | D1   | D0   |  |  |  |

| FDRB     | TWAB                                     | TFRB | IR1 | IR0 | MCS2 | MCS1 | MCS0 |  |  |  |

| 0        | 1                                        | 1    | 0   | 0   | 0    | 1    | 1    |  |  |  |

#### 5.1.1 Master Clock Select

| BIT | R/W | RST | NAME | DESCRIPTION                                              |

|-----|-----|-----|------|----------------------------------------------------------|

| 0   | R/W | 1   | MCS0 | Master Clock Select: Selects the ratio between the input |

| 1   | R/W | 1   | MCS1 | I <sup>2</sup> S sample frequency and the input clock.   |

| 2   | R/W | 0   | MCS2 |                                                          |

The DDXi-2161 and DDXi-2101 (**DDXi-21x1**) will support sample rates of 32kHz, 44.1kHz, 48Khz, 88.2kHz, and 96kHz. The external clock frequency provided to the XTI pin must be a multiple of the input sample frequency (fs). The correlation between the input clock and the input sample rate is determined by the status of the MCSx bits and the IR (Input Rate) register bits. The MCSx bits determine the PLL factor generating the internal clock and the IR bit determines the oversampling ratio used internally.

Table 3 - IR and MCS Settings for Input Sample Rate and Clock Rate

| Input Sample Rate fs (kHz)  | IR  |       | М     | CS (20) |       |       |

|-----------------------------|-----|-------|-------|---------|-------|-------|

| input Sample Nate is (Ki12) | IIX | 1xx   | 011   | 010     | 001   | 000   |

| 32, 44.1, 48                | 00  | 128fs | 256fs | 384fs   | 512fs | 768fs |

| 88.2, 96                    | 01  | 64fs  | 128fs | 192fs   | 256fs | 384fs |

| 176.4, 192                  | 10  | 64fs  | 128fs | 192fs   | 256fs | 384fs |

5.1.2 Interpolation Ratio Select

| _   |     |     |         |                                                                                                                   |

|-----|-----|-----|---------|-------------------------------------------------------------------------------------------------------------------|

| BIT | R/W | RST | NAME    | DESCRIPTION                                                                                                       |

| 43  | R/W | 00  | IR (10) | Interpolation Ratio Select: Selects internal interpolation ratio based on input I <sup>2</sup> S sample frequency |

The DDXi-21x1 has variable interpolation (re-sampling) settings such that internal processing and DDX output rates remain consistent. The first processing block interpolates by either 2 times or 1 time (pass-through) or provides a down-sample by a factor of 2. The IR bits determine the re-sampling ratio of this interpolation.

Table 4 - IR bit settings as a function of Input Sample Rate

| Input Sample Rate Fs (kHz) | IR (1,0) | 1 <sup>st</sup> Stage Interpolation Ratio |

|----------------------------|----------|-------------------------------------------|

| 32                         | 00       | 2 times over-sampling                     |

| 44.1                       | 00       | 2 times over-sampling                     |

| 48                         | 00       | 2 times over-sampling                     |

| 88.2                       | 01       | Pass-Through                              |

| 96                         | 01       | Pass-Through                              |

| 176.4                      | 10       | Down-sampling by 2                        |

| 192                        | 10       | Down-sampling by 2                        |

5.1.3 Thermal Warning Recovery Bypass

| BIT | R/W | RST | NAME | DESCRIPTION                           |

|-----|-----|-----|------|---------------------------------------|

| 5   | R/W | 1   | TWRB | Thermal-Warning Recovery Bypass:      |

|     |     |     |      | 0 – Thermal warning Recovery enabled  |

|     |     |     |      | 1 – Thermal warning Recovery disabled |

If the Thermal Warning Adjustment is enabled (TWAB=0), then the Thermal Warning Recovery (TWRB=0) will remove the attenuation when the warning condition is deasserted . If TWRB=1 and TWAB=0, when thermal warning is deasserted the Thermal Warning Adjustment will remain in effect until TWRB is changed to zero or the device is reset.

5.1.4 Thermal Warning Adjustment Bypass

| BIT | R/W | RST | NAME | DESCRIPTION                                                                  |

|-----|-----|-----|------|------------------------------------------------------------------------------|

| 6   | R/W | 1   | TWAB | Thermal-Warning Adjustment Bypass:<br>0 – Thermal warning adjustment enabled |

|     |     |     |      | 1 – Thermal warning adjustment disabled                                      |

The on-chip DDXi-21x1 Power Output block provides feedback to the digital controller using inputs to the Power Control block. The TWARN input is used to indicate a thermal warning condition. When TWARN is asserted (set to 0) for a period greater than 400ms, the power control block will reduce the output level (default = -3dB) in an attempt to eliminate the thermal warning condition. The amount of attenuation under this condition can be controlled by the Thermal Warning – Post Scale value, which is located in the coefficient RAM, address 0x37. See section 6.6 for modifying this value. After the thermal warning volume adjustment is applied, when TWARN is de-asserted the adjustment is removed if TWRB=0.

5.1.5 Fault Detect Recovery Bypass

| ••  | . aait D | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Jooroly Bypaco |                                    |

|-----|----------|-----------------------------------------|----------------|------------------------------------|

| BIT | R/W      | RST                                     | NAME           | DESCRIPTION                        |

| 7   | R/W      | 0                                       | FDRB           | Fault-Detect Recovery Bypass:      |

|     |          |                                         |                | 0 – Fault Detect Recovery enabled  |

|     |          |                                         |                | 1 – Fault Detect Recovery disabled |

The DDX Power block provides feedback to the digital controller using inputs to the Power Control block. The FAULT input is used to signal a fault condition (either over-current or thermal). When FAULT is asserted (set to 0), the power-block will be immediately disabled, the power control block will then attempt automatic recovery from the fault by asserting the tri-state signal in a sequence to reset the fault and retest the fault status. The sequence period, from fault to recovery attempt, can range from 0.1 milliseconds to 1 second as defined by the Fault-Detect Recovery Constant register (FDRC registers 29-2Ah). This sequence is repeated for as long as the fault condition exists. This feature is enabled by default but can be disabled by setting the FDRB control bit to 1. If Fault-Detect Recovery is disabled (not recommended), an output stage FAULT will cause a shut-down condition, which must be reset either by toggling the external reset pin or via a VCC power cycle to the IC.

5.2 Configuration Register B (Address 01h)

|      | • • • • • • • • • • • • • • • • • • • • |       | 3     |      |      |      |      |

|------|-----------------------------------------|-------|-------|------|------|------|------|

| D7   | D6                                      | D5    | D4    | D3   | D2   | D1   | D0   |

| C2IM | C1IM                                    | DSCKE | SAIFB | SAI3 | SAI2 | SAI1 | SAI0 |

| 1    | 0                                       | 0     | 0     | 0    | 0    | 0    | 0    |

5.2.1 Serial Audio Input Interface Format

| Ī | BIT | R/W | RST  | NAME     | DESCRIPTION                                                                                                       |

|---|-----|-----|------|----------|-------------------------------------------------------------------------------------------------------------------|

|   | 30  | R/W | 0000 | SAI (30) | Serial Audio Input Interface Format: Determines the interface format of the input serial digital audio interface. |

#### **Serial Data Interface**

The DDXi-21x1 serial audio input was designed to interface with standard digital audio components and to accept a number of serial data formats. The DDXi-21x1 always acts as a slave when receiving audio input from standard digital audio components. Serial data for two channels is provided using 3 input pins: left/right clock LRCKI (pin 33), serial clock BICKI (pin 31), and serial data 1 & 2 SDI12 (pin 32).

The SAI register (Configuration Register B - 01h, Bits D3-D0) and the SAIFB register (Configuration Register B - 01h, Bit D4) are used to specify the serial data format. The default serial data format is I<sup>2</sup>S, MSB-First. Available formats are shown in Figure 24 and the tables that follow.

Figure 24 - Serial Audio Input and Output Formats

For example, SAI=1110 and SAIFB=1 would specify Right-Justified 16-bit data, LSB-First.

Table 6 below lists the serial audio input formats supported by the DDXi-21x1 as related to BICKI = 32/48/64fs, where the sampling rate fs = 32/44.1/48/88.2/96/176.4/192 kHz.

Table 5 - First Bit Selection Table

| SAIFB | Format    |

|-------|-----------|

| 0     | MSB-First |

| 1     | LSB-First |

Note: Serial input and output formats are specified distinctly.

Table 6 - Supported Serial Audio Input Formats

| BICKI | SAI (30) | SAIFB | Interface Format                      |  |

|-------|----------|-------|---------------------------------------|--|

| 32fs  | 1100     | Χ     | I <sup>2</sup> S 15bit Data           |  |

| 3215  | 1110     | Х     | Left/Right-Justified 16bit Data       |  |

|       | 0100     | Χ     | I <sup>2</sup> S 23bit Data           |  |

|       | 0100     | Χ     | I <sup>2</sup> S 20bit Data           |  |

|       | 1000     | Χ     | I <sup>2</sup> S 18bit Data           |  |

|       | 0100     | 0     | MSB First I <sup>2</sup> S 16bit Data |  |

|       | 1100     | 1     | LSB First I <sup>2</sup> S 16bit Data |  |

|       | 0001     | Χ     | Left-Justified 24bit Data             |  |

| 48fs  | 0101     | Χ     | Left-Justified 20bit Data             |  |

|       | 1001     | Х     | Left-Justified 18bit Data             |  |

|       | 1101     | Χ     | Left-Justified 16bit Data             |  |

|       | 0010     | Х     | Right-Justified 24bit Data            |  |

|       | 0110     | Χ     | Right-Justified 20bit Data            |  |

|       | 1010     | Χ     | Right-Justified 18bit Data            |  |

|       | 1110     | Х     | Right-Justified 16bit Data            |  |

|       | 0000     | Χ     | I <sup>2</sup> S 24bit Data           |  |

|       | 0100     | Χ     | I <sup>2</sup> S 20bit Data           |  |

|       | 1000     | Χ     | I <sup>2</sup> S 18bit Data           |  |

|       | 0000     | 0     | MSB First I <sup>2</sup> S 16bit Data |  |

|       | 1100     | 1     | LSB First I <sup>2</sup> S 16bit Data |  |

|       | 0001     | Χ     | Left-Justified 24bit Data             |  |

| 64fs  | 0101     | Х     | Left-Justified 20bit Data             |  |

|       | 1001     | Х     | Left-Justified 18bit Data             |  |

|       | 1101     | Χ     | Left-Justified 16bit Data             |  |

|       | 0010     | Χ     | Right-Justified 24bit Data            |  |

|       | 0110     | Χ     | Right-Justified 20bit Data            |  |

|       | 1010     | Χ     | Right-Justified 18bit Data            |  |

|       | 1110     | Χ     | Right-Justified 16bit Data            |  |

Table 7 - Serial Input Data Timing characteristics (Fs = 32 to 192kHz)

| BICKI FREQUENCY (slave mode)             | 12.5MHz max. |

|------------------------------------------|--------------|

| BICKI pulse width low (T0) (slave mode)  | 40 ns min.   |

| BICKI pulse width high (T1) (slave mode) | 40 ns min.   |

| BICKI active to LRCKI edge delay (T2)    | 20 ns min.   |

| BICKI active to LRCKI edge delay (T3)    | 20 ns min.   |

| SDI valid to BICKI active setup (T4)     | 20 ns min.   |

| BICKI active to SDI hold time (T5)       | 20 ns min.   |

Figure 25 - Serial Input Data Timing Characteristics

5.2.2 Delay Serial Clock Enable

| • | V.  | Doing O | oriai Or | OOK Ellabio |                                                          |

|---|-----|---------|----------|-------------|----------------------------------------------------------|

|   | BIT | R/W     | RST      | NAME        | DESCRIPTION                                              |

|   | 5   | R/W     | 0        | DSCKE       | Delay Serial Clock Enable:                               |

|   |     |         |          |             | 0 – No serial clock delay                                |

|   |     |         |          |             | 1 – Serial clock delay by 1 core clock cycle to tolerate |

|   |     |         |          |             | anomalies in some I2S master devices                     |

5.2.3 Channel Input Mapping

| 0.2.0 | Onamic | ı iiipat | mapping |                                                                                                                                 |

|-------|--------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------|

| BIT   | R/W    | RST      | NAME    | DESCRIPTION                                                                                                                     |

| 6     | R/W    | 0        | C1IM    | 0 – Processing channel 1 receives Left I <sup>2</sup> S Input<br>1 – Processing channel 1 receives Right I <sup>2</sup> S Input |

| 7     | R/W    | 1        | C2IM    | 0 – Processing channel 2 receives Left I <sup>2</sup> S Input<br>1 – Processing channel 2 receives Right I <sup>2</sup> S Input |

Each channel received via I<sup>2</sup>S can be mapped to any internal processing channel via the Channel Input Mapping registers. This allows for flexibility in processing. The default settings of these registers map each I<sup>2</sup>S input channel to its corresponding processing channel.

5.3 Configuration Register C (Address 02h)

| D7 | D6   | D5   | D4   | D3   | D2   | D1  | D0  |

|----|------|------|------|------|------|-----|-----|

|    | CSZ4 | CSZ3 | CSZ2 | CSZ1 | CSZ0 | OM1 | OM0 |

|    | 1    | 0    | 0    | 0    | 0    | 1   | 0   |

5.3.1 DDX<sup>®</sup> Power Output Mode

| BIT | R/W | RST | NAME    | DESCRIPTION                                                                 |

|-----|-----|-----|---------|-----------------------------------------------------------------------------|

| 10  | R/W | 10  | OM (10) | DDX Power Output Mode:<br>Selects configuration of DDX <sup>®</sup> output. |

The DDX $^{\otimes}$  Power Output Mode selects how the DDX $^{\otimes}$  output timing is configured. The DDXi-21x1's recommended use is OM = 10. When OM=11 the CSZ bits determine the size of the DDX $^{\otimes}$  compensating pulse.

Table 8 - DDX<sup>®</sup> Output Modes

| OM (1,0) | Output Stage – Mode   |

|----------|-----------------------|

| 00       | Not Used              |

| 01       | Not Used              |

| 10       | DDXi-2101             |

| 11       | Variable Compensation |

5.3.2 DDX<sup>®</sup> Variable Compensating Pulse Size

| BIT | R/W | RST   | NAME     | DESCRIPTION                    |

|-----|-----|-------|----------|--------------------------------|

| 62  | R/W | 10000 | CSZ (40) | Compensating Pulse Size Select |

The DDX® variable compensating pulse size is not recommended to be used except in special circumstances. Contact Apogee applications for support when deciding to use this function.

Table 9 - DDX<sup>®</sup> Compensating Pulse

| CSZ (40) | Compensating Pulse Size                 |

|----------|-----------------------------------------|

| 00000    | O Clock period Compensating Pulse Size  |

| 00001    | 1 Clock period Compensating Pulse Size  |

|          |                                         |

| 10000    | 16 Clock period Compensating Pulse Size |

|          |                                         |

| 11111    | 31 Clock period Compensating Pulse Size |

5.4 Configuration Register D (Address 03h)

| D7  | D6  | D5  | D4  | D3  | D2   | D1   | D0  |

|-----|-----|-----|-----|-----|------|------|-----|

| SME | ZDE | DRC | BQL | PSL | DSPB | DEMP | HPB |

| 0   | 1   | 0   | 0   | 0   | 0    | 0    | 0   |

5.4.1 High-Pass Filter Bypass

| BIT | R/W | RST | NAME | DESCRIPTION                                                                                                       |

|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------------|

| 0   | R/W | 0   | HPB  | High-Pass Filter Bypass Bit.  0 – AC Coupling High Pass Filter Enabled  1 – AC Coupling High Pass Filter Disabled |

The DDXi-21x1 features an internal digital high-pass filter for the purpose of DC Blocking. The purpose of this filter is to prevent DC signals from passing through a DDX $^{\tiny{(8)}}$  amplifier. DC signals can cause speaker damage.

5.4.2 De-Emphasis

| BIT | R/W | RST | NAME | DESCRIPTION                                           |

|-----|-----|-----|------|-------------------------------------------------------|

| 1   | R/W | 0   | DEMP | De-emphasis:<br>0 – No De-emphasis<br>1 – De-emphasis |

By setting this bit to HIGH, or one (1), de-emphasis will implemented on all channels. DSPB (DSP Bypass, Bit D2, CFA) bit must be set to 0 for De-emphasis to function.

5.4.3 DSP Bypass

| BIT | R/W | RST | NAME | DESCRIPTION                                                                    |  |  |  |

|-----|-----|-----|------|--------------------------------------------------------------------------------|--|--|--|

| 2   | R/W | 0   | DSPB | DSP Bypass Bit: 0 – Normal Operation 1 – Bypass of EQ and Mixing Functionality |  |  |  |

Setting the DSPB bit bypasses all the EQ and Mixing functionality of the DDXi-2101 Core.

#### 5.4.4 Post-Scale Link

| BIT | R/W | RST | NAME | DESCRIPTION                                                                                                         |

|-----|-----|-----|------|---------------------------------------------------------------------------------------------------------------------|

| 3   | R/W | 0   | PSL  | Post-Scale Link: 0 – Each Channel uses individual Post-Scale value 1 – Each Channel uses Channel 1 Post-Scale value |

Post-Scale functionality is an attenuation placed after the volume control and directly before the conversion to PWM. Post-Scale can also be used to limit the maximum modulation index and therefore the peak current. A setting of 1 in the PSL register will result in the use of the value stored in Channel 1 post-scale for all three internal channels.

5.4.5 Biguad Coefficient Link

| BIT | R/W | RST | NAME | DESCRIPTION                                                                                              |

|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------|

| 4   | R/W | 0   | BQL  | Biquad Link: 0 – Each Channel uses coefficient values 1 – Each Channel uses Channel 1 coefficient values |

For ease of use, all channels can use the biquad coefficients loaded into the Channel 1 Coefficient RAM space by setting the BQL bit to 1. Therefore, any EQ updates only have to be performed once.

5.4.6 Dynamic Range Compression/Anti-Clipping Bit

| • • • • • • • • • • • • • • • • • • • • | <u> </u> |     | tange compression |                                                                                                                                   |

|-----------------------------------------|----------|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| BIT                                     | R/W      | RST | NAME              | DESCRIPTION                                                                                                                       |

| 5                                       | R/W      | 0   | DRC               | Dynamic Range Compression/Anti-Clipping 0 – Limiters act in Anti-Clipping Mode 1 – Limiters act in Dynamic Range Compression Mode |

Both limiters can be used in one of two ways, anti-clipping or dynamic range compression. When used in anti-clipping mode the limiter threshold values are constant and dependent on the limiter settings. In dynamic range compression mode the limiter threshold values vary with the volume settings allowing a nighttime listening mode that provides a reduction in the dynamic range regardless of the volume level.

#### 5.4.7 Zero-Detect Mute Enable

| • | - · · · · · · - | -0.0 -0. | oot mat | 5 <b>=</b> 114510 |                                                                              |

|---|-----------------|----------|---------|-------------------|------------------------------------------------------------------------------|

| ſ | BIT             | R/W      | RST     | NAME              | DESCRIPTION                                                                  |

|   | 6               | R/W      | 1       | ZDE               | Zero-Detect Mute Enable: Setting of 1 enables the automatic zero-detect mute |

Setting the ZDE bit enables the zero-detect automatic mute. When ZDE=1, the zero-detect circuit looks at the input data to each processing channel after the channel-mapping block. If any channel receives 2048 consecutive zero value samples (regardless of fs) then that individual channel is muted (ZDE=1).

#### 5.4.8 Sub-Mix Enable

| BIT | R/W | RST | NAME | DESCRIPTION                                                                              |  |

|-----|-----|-----|------|------------------------------------------------------------------------------------------|--|

| 7   | R/W | 0   | SME  | Sub-Mix Enable: 0 – Sub Mix into Left/Right Disabled 1 – Sub Mix into Left/Right Enabled |  |

Setting the SME bit enables a scaled-mix of the content from the Sub channel (i.e. channel 3) into the main Left & Right channels (i.e. channels 1 & 2). The Sub-Mix resides post-volume & gain compression processing.

5.5 Configuration Register E (Address 04h)

|     |     | ,   |      |     | 1    |     | -,   |

|-----|-----|-----|------|-----|------|-----|------|

| D7  | D6  | D5  | D4   | D3  | D2   | D1  | D0   |

| SVE | ZCE | RES | PWMS | AME | NSBW | MPC | MPCV |

| 1   | 1   | 0   | 0    | 0   | 0    | 1   | 0    |

#### 5.5.1 Max Power Correction Variable

| BIT | R/W | RST | NAME | DESCRIPTION                                                                                           |

|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------|

| 0   | R/W | 0   | MPCV | Max Power Correction Variable: 0 – Use Standard MPC Coefficient 1 – Use MPCC bits for MPC Coefficient |

By enabling MPC and setting MPCV = 1, the max power correction becomes variable. By adjusting the MPCC registers (address 0x27-0x28) it becomes possible to adjust the THD at maximum unclipped power to a lower value for a particular application.

#### 5.5.2 Max Power Correction