### **FEATURES**

#### n Video Decoder

- Ÿ Supports NTSC, PAL and SECAM video input formats

- Ÿ 2D NTSC and PAL comb-filter for Y/C separation of CVBS input

- Ÿ Single S-video and/or multiple CVBS inputs

- Ÿ Supports closed-caption and V-chip

- Ÿ ACC, AGC, and DCGC (Digital Chroma Gain Control)

#### n Analog Input

- Ÿ Supports RGB input format from PC, camcorders and GPS

- Ϋ́ Supports video input 480i, 480p, 576i, 576p, 720p, 1080i; RGB input resolution in 640x480, 800x480, and 800x600 (SVGA)

- Ÿ 3-channel low-power 10-bit ADCs integration for RGB

- Ÿ Supports RGB composite sync input (CSYNC), SOY, SOG, HSYNC, and VSYNC

- Ÿ On-chip clock synthesizer and PLL

- Ÿ Auto-position adjustment, auto-phase adjustment, auto-gain adjustment, and auto-mode detection

#### n Digital Input

Ÿ Supports ITU656 input, progressive ITU656 compatible input format

#### n Color Engine

- Ÿ Brightness, contrast, saturation, and hue adjustment

- Ÿ 9-tap programmable multi-purpose FIR (Finite Impulse Response) filter

- Ÿ Differential 3-band peaking engine

- Ÿ Luminance Transient Improvement (LTI)

- Ÿ Chrominance Transient Improvement (CTI)

- Ÿ Black Level Extension (BLE)

- Ÿ White Level Extension (WLE)

- Ÿ Favor Color Compensation (FCC)

- ÿ 3-channel gamma curve adjustment

#### n Scaling Engine/TCON

- Ÿ Supports analog panels with the resolution of 960x234, 1200x234, 1400x234, and more

- Ÿ Supports various displaying modes

- Ÿ Supports horizontal panorama scaling

#### n Miscellaneous

- Ÿ Built-in MCU

- Ÿ 3-wire serial bus interface for configuration setup

- Ÿ Built-in VCOM DC level adjusting circuits

- Built-in internal OSD with 256 programmable fonts, 16-color palettes, and 12-bit color resolution

The programmable of the programmabl

- 3-channel low-power 8-bit DAC integration for RGB output, dynamic range 0.1-4.9V

- Ÿ Built-in step-down PWM circuits for input 2.5V

- Ÿ Built-in VCOM DC/AC level adjustment circuit

- Ÿ Supports external OSD

- Ÿ Spread spectrum clocks

- Ÿ Optional 3.3V / 5V output pads with programmable driving current

- Ÿ 128-pin PQFP package

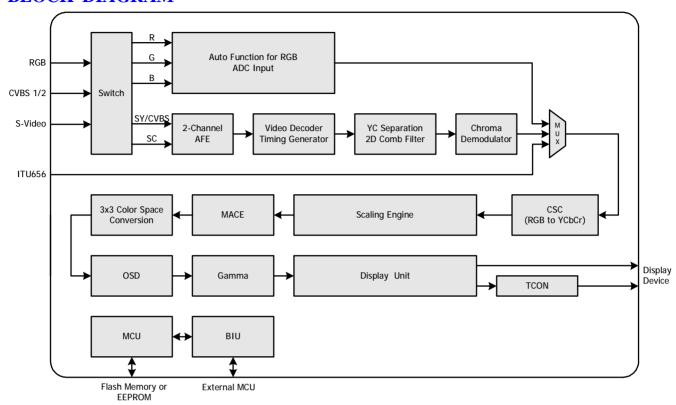

#### **BLOCK DIAGRAM**

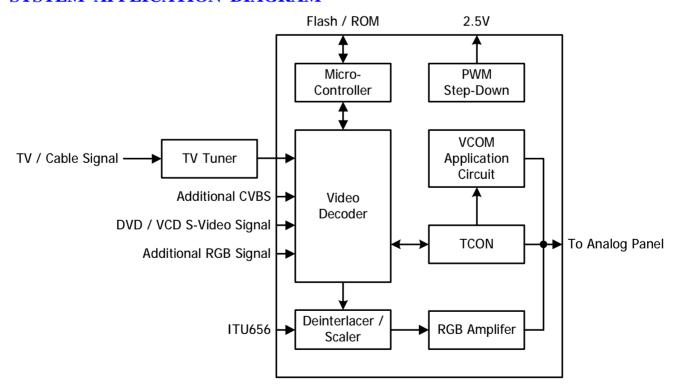

## SYSTEM APPLICATION DIAGRAM

### **GENERAL DESCRIPTION**

The MST716A is a high quality ASIC for NTSC/PAL/SECAM car TV application. It receives analog NTSC/PAL/SECAM CVBS and S-Video inputs from TV tuners, DVD or VCR sources, including weak and distorted signals, as well as analog RGB input from GPS systems. Automatic gain control (AGC) and 8-bit 3-channel A/D converters provide high resolution video quantization. With automatic video source and mode detection, users can easily switch and adjust variety of signal sources. Multiple internal adaptive PLLs precisely extract pixel clock from video source and perform sharp color demodulation. Built-in line-buffer supports adaptive 2-D comb-filter, 2-D sharpening, and synchronization stabler in a condense manner. The output format of MST716A supports 3.5"~7" analog TFT-LCD modules.

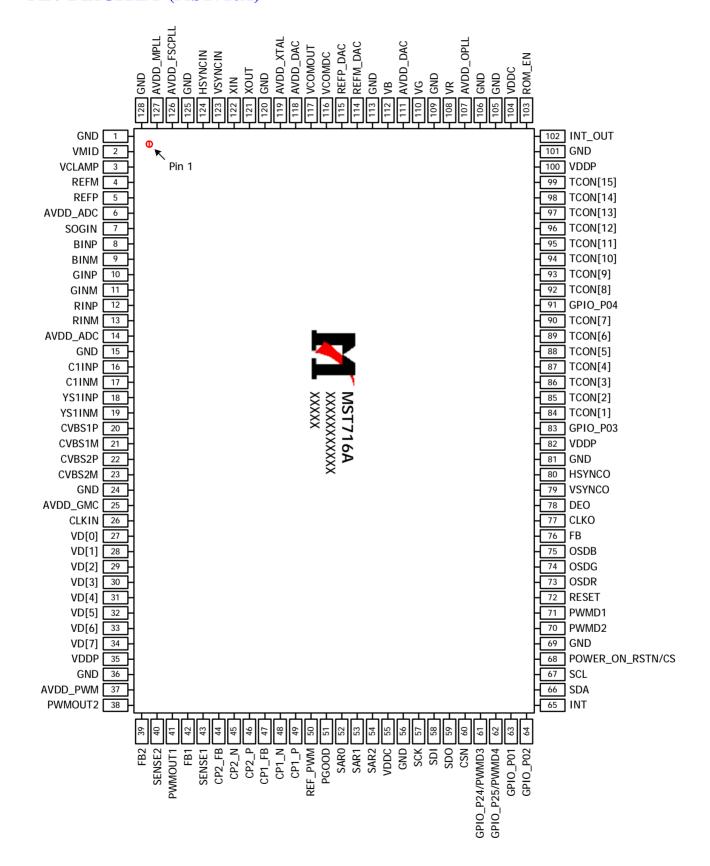

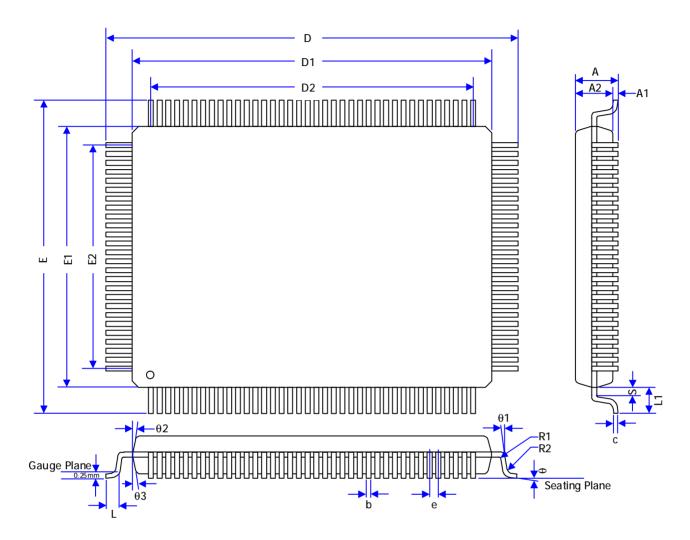

# PIN DIAGRAM (MST716A)

PIN DESCRIPTION

# emiconductor **emiconductor**

# Analog Interface

| Pin Name | Pin Type                                | Function                                                                                     | Pin |

|----------|-----------------------------------------|----------------------------------------------------------------------------------------------|-----|

| VMID     |                                         | Mid-Scale Voltage Bypass                                                                     | 2   |

| VCLAMP   |                                         | CVBS/YC Mode Clamp Voltage Bypass                                                            | 3   |

| REFM     |                                         | Internal ADC Bottom De-coupling Pin                                                          | 4   |

| REFP     |                                         | Internal ADC Top De-coupling Pin                                                             | 5   |

| SOGIN    | Analog Input                            | Sync-on-Green slicer input                                                                   | 7   |

| BINP     | Analog Input                            | Analog B Input of VGA                                                                        | 8   |

| BINM     | Analog Input                            | Reference Ground for Analog B Input of VGA                                                   | 9   |

| GINP     | Analog Input                            | Analog G Input of VGA                                                                        | 10  |

| GINM     | Analog Input                            | Reference Ground for Analog G Input of VGA                                                   | 11  |

| RINP     | Analog Input                            | Analog R Input of VGA                                                                        | 12  |

| RINM     | Analog Input                            | Reference Ground for Analog R Input of VGA                                                   | 13  |

| C1INP    | Analog Input                            | Analog Chroma Input for TV S-Video1 / Analog Composite Input of TV CVBS4                     |     |

| C1INM    | Analog Input                            | Reference Ground for Analog Chroma Input of TV S-Video1 / Analog Composite Input of TV CVBS4 |     |

| YS1INP   | Analog Input                            | Analog Luma Input of TV S-Video1 / Analog Composite Input of TV CVBS3                        |     |

| YS1INM   | Analog Input                            | Reference Ground for Analog Luma Input of TV S-Video1 / Analog Composite Input of TV CVBS3   |     |

| CVBS1P   | Analog Input                            | Analog Composite Input for TV CVBS1                                                          | 20  |

| CVBS1M   | Analog Input                            | Reference Ground for Analog Composite Input of TV CVBS1                                      |     |

| CVBS2P   | Analog Input                            | Analog Composite Input for TV CVBS2                                                          |     |

| CVBS2M   | Analog Input                            | Reference Ground for Analog Composite Input of TV CVBS2                                      |     |

| HSYNCIN  | Schmitt Trigger Input<br>w/ 5V-tolerant | HSYNC / Composite Sync for VGA Input                                                         |     |

| VSYNCIN  | Schmitt Trigger Input<br>w/ 5V-tolerant | VSYNC for VGA Input                                                                          | 123 |

# Digital Video Input Interface

| Pin Name | Pin Type            | Function                        | Pin   |

|----------|---------------------|---------------------------------|-------|

| CLKIN    | Input w/5V-tolerant | Sample Clock ITU656 Video Input | 26    |

| VD[7:0]  | Input w/5V-tolerant | ITU656 Video Data bus           | 34-27 |

## Analog Panel Output Interface

| Pin Name   | Pin Type      | Function                                                   | Pin             |

|------------|---------------|------------------------------------------------------------|-----------------|

| VR         | Analog Output | Red Channel Output 4.0 Vp-p                                | 108             |

| VG         | Analog Output | Green Channel Output 4.0 Vp-p                              | 110             |

| VB         | Analog Output | Blue Channel Output 4.0 Vp-p                               | 112             |

| REFM_DAC   |               | DAC Bottom Reference Voltage Decoupling Cap. 1uF to Ground | 114             |

| REFP_DAC   |               | DAC Top Reference Voltage Decoupling Cap. 1uF to Ground    | 115             |

| CLKO       | Output        | Display Clock Output                                       | 77              |

| DEO        | Output        | Display Enable Output                                      | 78              |

| VSYNCO     | Output        | Vertical Sync Output                                       | 79              |

| HSYNCO     | Output        | Horizontal Sync Output                                     | 80              |

| TCON[15:1] | Output        | TCON Output                                                | 99-92,<br>90-84 |

## **External OSD Interface**

| Pin Name | Pin Type             | Function                     | Pin |

|----------|----------------------|------------------------------|-----|

| OSDR     | Input w/ 5V-tolerant | External OSD R-channel Input | 73  |

| OSDG     | Input w/ 5V-tolerant | External OSD R-channel Input | 74  |

| OSDB     | Input w/ 5V-tolerant | External OSD R-channel Input | 75  |

| FB       | Input w/ 5V-tolerant | External Fast-Blank Input    | 76  |

## **VCOM** Interface

| Pin Name | Pin Type      | Function                                         | Pin |

|----------|---------------|--------------------------------------------------|-----|

| VCOMDC   | Analog Output | Reference DC Voltage Output for Common Amplifier | 116 |

| VCOMOUT  | Analog Output | Pulse Output for Common Voltage.                 | 117 |

# Switching Power and PWM Interface

| Pin Name | Pin Type     | Function                                                     | Pin |

|----------|--------------|--------------------------------------------------------------|-----|

| PWMOUT2  | Output       | Switching Pulse Output for DC-DC Converter                   | 38  |

| FB2      | Analog Input | Error Voltage Feedback Input Pin for PWM2;<br>voltage = 1.2V | 39  |

| SENSE2   | Analog Input | Sense Circuit Connection for PWM2                            | 40  |

| PWMOUT1  | Output       | Switching Pulse Output for DC-DC Converter                   | 41  |

| FB1      | Analog Input | Error Voltage Feedback Input Pin for PWM1;<br>voltage = 1.2V | 42  |

| Pin Name | Pin Type     | Function                                                        | Pin |

|----------|--------------|-----------------------------------------------------------------|-----|

| SENSE1   | Analog Input | Sense Circuit Connection for PWM1                               | 43  |

| CP2_FB   | Analog Input | Error Voltage Feedback Input Pin for CP2; voltage = 1.2V        | 44  |

| CP2_N    | Output       | Charge Pump Negative Pulse for DC-DC Negative Voltage Converter | 45  |

| CP2_P    | Output       | Charge Pump Positive Pulse for DC-DC Negative Voltage Converter | 46  |

| CP1_FB   | Analog Input | Error Voltage Feedback Input Pin for CP1; voltage = 1.2V        | 47  |

| CP1_N    | Output       | Charge Pump Negative Pulse for DC-DC Positive Voltage Converter | 48  |

| CP1_P    | Output       | Charge Pump Positive Pulse for DC-DC Positive Voltage Converter | 49  |

| REF_PWM  |              | PWM Reference; voltage = 2.4V                                   | 50  |

| PGOOD    | Output       | Power Good Detector                                             | 51  |

# Internal MCU Interface with Serial Flash Memory

| Pin Name         | Pin Type             | Function                                                 | Pin |  |

|------------------|----------------------|----------------------------------------------------------|-----|--|

| SAR2             | Analog Input         | SAR Low Speed ADC Input 2                                |     |  |

| SAR1             | Analog Input         | SAR Low Speed ADC Input 1                                | 53  |  |

| SAR0             | Analog Input         | SAR Low Speed ADC Input 0                                | 52  |  |

| SCK              | Output               | SPI Interface Sampling Clock                             | 57  |  |

| SDI              | Output               | SPI Interface Data-In                                    | 58  |  |

| SDO              | Input w/ 5V-tolerant | SPI Interface Data-Out                                   | 59  |  |

| CSN              | Output               | SPI Interface Chip Select                                | 60  |  |

| GPIO_P01         | I/O w/ 5V-tolerant   | General Purpose Input/Output; 4mA driving strength       | 63  |  |

| GPIO_P02         | I/O w/ 5V-tolerant   | General Purpose Input/Output; 4mA driving strength       | 64  |  |

| INT              | Input                | Interrupt Input for IR Receiver                          |     |  |

| SDA              | I/O w/ 5V-tolerant   | 3-Wire Serial Bus Data                                   |     |  |

| SCL              | Input w/ 5V-tolerant | 3-Wire Serial Bus Clock                                  |     |  |

| POWER_ON_RSTN/CS | Input w/ 5V-tolerant | Power On Reset Signal / Chip Selection for 3-wire Serial |     |  |

| GPIO_P03         | I/O w/ 5V-tolerant   | General Purpose Input/Output; 4mA driving strength       | 83  |  |

| GPIO_P04         | I/O w/ 5V-tolerant   | General Purpose Input/Output; 4mA driving strength       | 91  |  |

### Misc. Interface

| Pin Name       | Pin Type                                | Function                                                                                                         | Pin |

|----------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|

| RESET          | Schmitt Trigger Input<br>w/ 5V-tolerant | Hardware Reset; active high                                                                                      |     |

| XIN            | Analog Input                            | Crystal Oscillator Input                                                                                         | 122 |

| XOUT           | Analog Output                           | Crystal Oscillator Output                                                                                        | 121 |

| GPIO_P24/PWMD3 | Output                                  | General Purpose Input/Output; 4mA driving strength/ Pulse Width Modulation Output; 4mA driving strength          |     |

| GPIO_P25/PWMD4 | Output                                  | General Purpose Input/Output; 4mA driving<br>strength/<br>Pulse Width Modulation Output; 4mA driving<br>strength |     |

| PWMD2          | Output                                  | Pulse Width Modulation Output; 4mA driving strength                                                              | 70  |

| PWMD1          | Output                                  | Pulse Width Modulation Output; 4mA driving strength                                                              | 71  |

| INT_OUT        | Output                                  | Mode Detection Interrupt Output                                                                                  |     |

| ROM_EN         | Input                                   | Internal ROM Enable.  0: Disable.  1: Enable.                                                                    | 103 |

### **Power Pins**

| Pin Name    | Pin Type      | Function                   | Pin                                                                     |

|-------------|---------------|----------------------------|-------------------------------------------------------------------------|

| AVDD_ADC    | 2.5V Power    | ADC Power                  | 6, 14                                                                   |

| AVDD_GMC    | 5V Power      | GMC Power                  | 25                                                                      |

| AVDD_PWM    | 5V Power      | PWM Power                  | 37                                                                      |

| AVDD_OPLL   | 2.5V Power    | OPLL Power                 | 107                                                                     |

| AVDD_DAC    | 5V Power      | Voltage DAC Power          | 111, 118                                                                |

| AVDD_XTAL   | 5V Power      | XTAL Power                 | 119                                                                     |

| AVDD_FSCPLL | 2.5V Power    | FSCPLL Power               | 126                                                                     |

| AVDD_MPLL   | 2.5V Power    | MPLL Power                 | 127                                                                     |

| VDDC        | 2.5V Power    | Digital Core Power         | 55, 104                                                                 |

| VDDP        | 3.3V/5V Power | Digital Input/Output Power | 35, 82, 100                                                             |

| GND         | Ground        | Ground                     | 1, 15, 24, 36, 56, 69,<br>81, 101, 105, 106, 109,<br>113, 120, 125, 128 |

### **ELECTRICAL SPECIFICATIONS**

## **Absolute Maximum Ratings**

| Parameter                                                | Symbol                | Min  | Тур | Max           | Units |

|----------------------------------------------------------|-----------------------|------|-----|---------------|-------|

| 5.0V Supply Voltages                                     | $V_{VDD\_50}$         | -0.3 |     | 5.5           | ٧     |

| 3.3V Supply Voltages                                     | $V_{VDD\_33}$         | -0.3 |     | 3.6           | ٧     |

| 2.5V Supply Voltages                                     | $V_{VDD\_25}$         | -0.3 |     | 2.75          | ٧     |

| Input Voltage (5V tolerant inputs)                       | V <sub>IN5Vtol</sub>  | -0.3 |     | 5.0           | ٧     |

| Input Voltage (non 5V tolerant inputs)                   | V <sub>IN</sub>       | -0.3 |     | $V_{VDD\_33}$ | ٧     |

| Ambient Operating Temperature (commercial use)           | T <sub>A</sub>        | 0    |     | 70            | °C    |

| Ambient Operating Temperature (extended temp. range)     | T <sub>A</sub>        | -20  |     | 80            | °C    |

| Storage Temperature                                      | T <sub>STG</sub>      | -40  |     | 125           | °C    |

| Junction Temperature                                     | TJ                    |      |     | 125           | °C    |

| Thermal Resistance (Junction to Air) Natural Conversion  | $\theta_{JA}$         |      | TBD |               | °C/W  |

| Thermal Resistance (Junction to Case) Natural Conversion | $\theta_{	extsf{JC}}$ |      | TBD |               | °C/W  |

Note: Stress above those listed under Absolute Maximum Rating may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions outside of those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

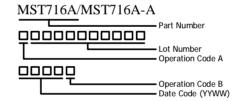

#### ORDERING GUIDE

| Model        | Temperature<br>Range | Package<br>Description | Package<br>Option |

|--------------|----------------------|------------------------|-------------------|

| MST716A      | 0°C to +70°C         | PQFP                   | 128               |

| MST716A-A    | -20°C to +80°C       | PQFP                   | 128               |

| MST716A-LF   | 0°C to +70°C         | PQFP                   | 128               |

| MST716A-A-LF | -20°C to +80°C       | PQFP                   | 128               |

Note: Product suffix "-LF" represents lead-free version and "-A" represents extended temperature range.

#### MARKING INFORMATION

#### **DISCLAIMER**

MSTAR SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. NO RESPONSIBILITY IS ASSUMED BY MSTAR SEMICONDUCTOR ARISING OUT OF THE APPLICATION OR USER OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

Electrostatic charges accumulate on both test equipment and human body and can discharge without detection. MST716A comes with ESD protection circuitry; however, the device may be permanently damaged when subjected to high energy discharges. The device should be handled with proper ESD precautions to prevent malfunction and performance degradation.

#### **REVISION HISTORY**

| Document       | Description       | Date     |

|----------------|-------------------|----------|

| MST716A_ds_v01 | Ÿ Initial release | Nov 2005 |

# **MECHANICAL DIMENSIONS**

| Symbol | M    | lillimet  | er   | Inch  |       |       |

|--------|------|-----------|------|-------|-------|-------|

| Symbol | Min. | Min. Nom. |      | Min.  | Nom.  | Max.  |

| Α      | -    | 1         | 3.40 | -     | -     | 0.134 |

| A1     | 0.25 | 1         | -    | 0.010 | -     | -     |

| A2     | 2.50 | 2.72      | 2.90 | 0.098 | 0.107 | 0.114 |

| D      |      | 23.20     |      | 0.913 |       |       |

| D1     |      | 20.00     |      | 0.787 |       |       |

| D2     |      | 18.50     |      | 0.728 |       |       |

| Е      |      | 17.20     |      | 0.677 |       |       |

| E1     |      | 14.00     |      |       | 0.551 |       |

| E2     |      | 12.50     |      | 0.492 |       |       |

| R1     | 0.13 | -         | -    | 0.005 | -     | -     |

| R2     | 0.13 | -         | 0.30 | 0.005 | -     | 0.012 |

| Symbol             | M     | illimet | er       | Inch       |       |       |

|--------------------|-------|---------|----------|------------|-------|-------|

| Symbol             | Min.  | Nom.    | Max.     | Min.       | Nom.  | Max.  |

| θ                  | 0°    | 1       | 7°       | 0°         | -     | 7°    |

| θ1                 | 0°    | 1       | -        | 0°         | -     | -     |

| θ2, θ3<br>(Alloy)  |       | 7° Ref  |          | 7° Ref     |       |       |

| θ2, θ3<br>(Copper) |       | 15° Ref | f        | 15° Ref    |       |       |

| b                  | 0.170 | 0.200   | 0.270    | 0.007      | 0.008 | 0.011 |

| С                  | 0.11  | 0.15    | 0.23     | 0.004      | 0.006 | 0.009 |

| е                  | 0     | .50 BS0 | <b>.</b> | 0.020 BSC. |       |       |

| L                  | 0.73  | 0.88    | 1.03     | 0.029      | 0.035 | 0.041 |

| L1                 |       | 1.60 Re | f        | 0.063 Ref  |       |       |

| S                  | 0.20  | -       | -        | 0.008      | -     | -     |

## **REGISTER DESCRIPTION**

# General Control Register

| Genera                    | General Control Register |      |                                                                     |             |  |  |

|---------------------------|--------------------------|------|---------------------------------------------------------------------|-------------|--|--|

| Index                     | Name                     | Bits | Description                                                         |             |  |  |

| 00h                       | REGBK                    | 7:0  | Default: 0x00                                                       | Access: R/W |  |  |

|                           | XTAL_OK (RO)             | 7    | Crystal ready.  0: Embedded MCU.  1: External serial bus interface. |             |  |  |

|                           | MCU_SEL (RO)             | 6    |                                                                     |             |  |  |

|                           | -                        | 5:4  | Reserved.                                                           |             |  |  |

|                           | AINC                     | 3    | Serial bus address auto Increase. 0: Enable. 1: Disable.            |             |  |  |

|                           | -                        | 2    | Reserved.                                                           |             |  |  |

| 10: Register of Video Dec |                          |      |                                                                     |             |  |  |

| 01h ~                     |                          | 7:0  | Default : -                                                         | Access:-    |  |  |

| FFh                       | -                        | 7:0  | Reserved.                                                           |             |  |  |

# Scaler Register (Bank = 00, Registers 01h ~ 9Fh)

| Scaler Register (Bank=00, Registers 01h ~ 9Fh) |            |      |                                                                                                                                                                      |                 |  |

|------------------------------------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| Index                                          | Name       | Bits | Description                                                                                                                                                          |                 |  |

| 01h                                            | DBFC       | 7:0  | Default: 0x80                                                                                                                                                        | Access: R/W     |  |

|                                                | -          | 7:3  | Reserved.                                                                                                                                                            |                 |  |

|                                                | DBL[1:0]   | 2:1  | Double Buffer Load. 00: Keep old register value. 01: Load new data (auto reset to 00 when load finish). 10: Automatically load data at VSYNC blanking. 11: Reserved. |                 |  |

|                                                | DB_EN      | 0    | Double Buffer Enable. 0: Disable. 1: Enable.                                                                                                                         |                 |  |

| 02h                                            | ISELECT    | 7:0  | Default: 0x00                                                                                                                                                        | Access: R/W     |  |

|                                                | NIS        | 7    | No Input Source. 0: Input source active. 1: Input source inactive, output                                                                                            | ut is free-run. |  |

|                                                | STYPE[1:0] | 6:5  | -                                                                                                                                                                    |                 |  |

| Scaler | Register (Bank=00, Re | gisters ( | 01h ~ 9Fh)                                                                                                                                                                                                                                             |                   |  |

|--------|-----------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

| Index  | Name                  | Bits      | Description                                                                                                                                                                                                                                            |                   |  |

|        | COMP                  | 4         | CSYNC/SOG select (only useful w 0: CSYNC. 1: SOG.                                                                                                                                                                                                      | then STYPE = 00). |  |

|        | ICS                   | 3         | Input Color Space. 0: RGB. 1: YCbCr.                                                                                                                                                                                                                   |                   |  |

|        | IHSU                  | 2         | Input Sync Usage. When EXTVD=0: 0: Use HSYNC to perform mode detection, HSOUT from ADC to sample pixel. 1: Use HSYNC only. When EXTVD=1: 0: Normal. 1: Output black at blanking.                                                                       |                   |  |

|        | BYPASSMD              | 1         | By-Pass Mode for interlace-input-in                                                                                                                                                                                                                    | nterlace-output.  |  |

|        | EXTVD                 | 0         | 0: Select analog input (CVBS/S-Vi-<br>1: Select digital input (CCIR656).                                                                                                                                                                               |                   |  |

| 03h    | IPCTRL2               | 7:0       | Default : 0x18                                                                                                                                                                                                                                         | Access: R/W       |  |

|        | VDS_EN                | 7         | Input data double sample In CCIR input mode, 0: for horizontal output resolution less than 720 pixels. 1: for horizontal output resolution more than 720 pixels. In analog input mode, 0: half sample of input data. 1: original sample of input data. |                   |  |

|        | VDS_MTHD              | 6         | Input data double sample Method. 0: Using average. 1: Using advance GT filter.                                                                                                                                                                         |                   |  |

|        | IVDS                  | 5         | Input VSYNC Delay Select. 0: Delay 1/4 input HSYNC (recom: 1: No delay.                                                                                                                                                                                | mended).          |  |

|        | HES                   | 4         | Input HSYNC reference Edge Sele 0: From HSYNC leading edge, defa 1: From HSYNC tailing edge.                                                                                                                                                           |                   |  |

|        | VES                   | 3         | Input VSYNC reference Edge Selection: From VSYNC leading edge, defail: From VSYNC tailing edge.                                                                                                                                                        |                   |  |

|        | ESLS                  | 2         | Early Sample Line Select. 0: 8 lines. 1: 16 lines.                                                                                                                                                                                                     |                   |  |

|        | VWRP                  | 1         | Input image Vertical Wrap. 0: Disable. 1: Enable.                                                                                                                                                                                                      |                   |  |

|        | HWRP                  | 0         | Input image Horizontal Wrap. 0: Disable. 1: Enable.                                                                                                                                                                                                    |                   |  |

| 04h    | ISCTRL                | 7:0       | Default: 0x10                                                                                                                                                                                                                                          | Access: R/W       |  |

| Index | Name         | Bits | Description                                                                                 |                                       |  |

|-------|--------------|------|---------------------------------------------------------------------------------------------|---------------------------------------|--|

| mucx  | DDE          | 7    | Direct DE mode for CCIR input. 0: Disable direct DE. 1: Enable direct DE.                   |                                       |  |

|       | DEGR[2:0]    | 6:4  | DE or HSYNC post Glitch removal                                                             | I Range.                              |  |

|       | HSFL         | 3    | Input HSYNC Filter. 0: Filter off. 1: Filter on.                                            |                                       |  |

|       | ISSM         | 2    | Input Sync Sample Mode. 0: Normal. 1: Glitch-removal.                                       |                                       |  |

|       | MVD_SEL      | 1:0  | MVD mode Select 0: CVBS. 1: S-Video. 2: YCbCr. 3: RGB.                                      |                                       |  |

| 05h   | SPRVST_L     | 7:0  | Default : 0x10                                                                              | Access : R/W, DB                      |  |

|       | SPRVST[7:0]  | 7:0  | Image vertical sample start point, bits).                                                   | count by input HSYNC (lower 8         |  |

| 06h   | SPRVST_H     | 7:0  | Default : 0x00                                                                              | Access : R/W, DB                      |  |

|       | -            | 7:3  | Reserved.                                                                                   |                                       |  |

|       | SPRVST[10:8] | 2:0  | Image vertical sample start point, bits).                                                   | count by input HSYNC (higher 3        |  |

| 07h   | SPRHST_L     | 7:0  | Default : 0x01                                                                              | Access : R/W, DB                      |  |

|       | SPRHST[7:0]  | 7:0  | Image horizontal sample start point bits).                                                  | t, count by input dot clock (higher 8 |  |

| 08h   | SPRHST_H     | 7:0  | Default : 0x00                                                                              | Access : R/W, DB                      |  |

|       | -            | 7:3  | Reserved.                                                                                   |                                       |  |

|       | SPRGST[10:8] | 2:0  | Image horizontal sample start poin bits).                                                   | t, count by input dot clock (lower 3  |  |

| 09h   | SPRVDC_L     | 7:0  | Default : 0x10                                                                              | Access : R/W, DB                      |  |

|       | SPRVDC[7:0]  | 7:0  | Image vertical resolution (vertical lower 8 bits).                                          | display enable area count by line;    |  |

| 0Ah   | SPRVDC_H     | 7:0  | Default: 0x00                                                                               | Access : R/W                          |  |

|       | -            | 7:3  | Reserved.                                                                                   |                                       |  |

|       | SPRVDC[10:8] | 2:0  | Image vertical resolution (vertical display enable area count by line; higher 3 bits).      |                                       |  |

| 0Bh   | SPRHDC_L     | 7:0  | Default : 0x10                                                                              | Access: R/W                           |  |

|       | SPRHDC[7:0]  | 7:0  | Image horizontal resolution (horizontal display enable area count by pixel; lower 8 bits).  |                                       |  |

| 0Ch   | SPRHDC_L     | 7:0  | Default : 0x00                                                                              | Access: R/W                           |  |

|       | -            | 7:3  | Reserved.                                                                                   |                                       |  |

|       | SPRHDC[10:8] | 2:0  | Image horizontal resolution (horizontal display enable area count by pixel; higher 3 bits). |                                       |  |

| 0Dh   | LYL          | 7:0  | Default: 0x00                                                                               | Access: R/W                           |  |

| Scaler | Register (Bank=00, Re | gisters (                                                                               | 01h ~ 9Fh)                                                                         |                     |  |

|--------|-----------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------|--|

| Index  | Name                  | Bits                                                                                    | Description                                                                        |                     |  |

|        | -                     | 7:4                                                                                     | Reserved.                                                                          |                     |  |

|        | LYL[3:0]              | 3:0                                                                                     | Lock Y Line.                                                                       |                     |  |

| 0Eh    | INTLX                 | 7:0                                                                                     | Default: 0x00                                                                      | Access: -           |  |

|        | ITU_EXT_FIELD         | 7                                                                                       | Using External FIELD for ITU inte<br>0: Using EAV/SAV.<br>1: Using external FIELD. | erface.             |  |

|        | ITU_EXT_HS            | 6                                                                                       | Using External HSYNC for ITU in 0: Using EAV/SAV. 1: Using external HSYNC.         | terface.            |  |

|        | ITU_EXT_VS            | 5                                                                                       | Using External VSYNC for ITU in 0: Using EAV/SAV. 1: Using external VSYNC.         | terface.            |  |

|        | VDOE                  | 4                                                                                       | Video reference Edge (for non-stan                                                 | dard signal).       |  |

|        | INTLAC_LOCKAVG        | 3                                                                                       | Averaging Locking timing.                                                          |                     |  |

|        | LHC_MD                | 2                                                                                       | Long Horizontal Counter Mode. 1: On. 0: Off.                                       |                     |  |

|        | -                     | 1:0                                                                                     | Reserved.                                                                          |                     |  |

| 0Fh    | ASCTRL                | 7:0                                                                                     | Default: 0x90                                                                      | Access: R/W         |  |

|        | IVB (RO)              | 7                                                                                       | Input VSYNC Blanking status. 0: In display. 1: In blanking.                        |                     |  |

|        | DLINE[2:0]            | 6:4                                                                                     | Line buffer read delay in number of                                                | f lines.            |  |

|        | INTLAC_MANSTD         | 3                                                                                       | NTSC/PAL Manual Mode                                                               |                     |  |

|        | INTLAC_SETSTD         | 2                                                                                       | NTSC/PAL Setting in manual mode 0: NTSC. 1: PAL.                                   | e under run status. |  |

|        | UNDER (RO)            | 1                                                                                       | Under run status.                                                                  |                     |  |

|        | OVER (RO)             | 0                                                                                       | Over run status.                                                                   |                     |  |

| 10h    | COCTRL1               | 7:0                                                                                     | Default: 0x00                                                                      | Access: R/W         |  |

|        | -                     | 7:6                                                                                     | Reserved.                                                                          |                     |  |

|        | AVI_SEL               | 5                                                                                       | Analog Video Input Select. 0: PC. 1: Component analog video.                       |                     |  |

|        | DLYV                  | 4 Analog Delay line for component analog Video input. 0: Delay 1 line. 1: Do not delay. |                                                                                    | nalog Video input.  |  |

|        | CSC_MD                | 3                                                                                       |                                                                                    |                     |  |

|        | EXVS                  | 2                                                                                       | External VSYNC polarity (only use 0: Normal. 1: Invert.                            | ed when COVS is 1). |  |

| Scaler Register (Bank=00, Registers 01h ~ 9Fh) |               |      |                                                                                                                                                                                                                                                                                                         |                           |  |

|------------------------------------------------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|

| Index                                          | Name          | Bits | Description                                                                                                                                                                                                                                                                                             |                           |  |

|                                                | COV_SEL       | 1    | Coast VSYNC Select. 0: Internal VSEP. 1: External VSYNC.                                                                                                                                                                                                                                                |                           |  |

|                                                | CADC          | 0    | Coast to ADC. 0: Disable. 1: Enable.                                                                                                                                                                                                                                                                    |                           |  |

| 11h                                            | COCTRL2       | 7:0  | Default: 0x00                                                                                                                                                                                                                                                                                           | Access: R/W               |  |

|                                                | COST[7:0]     | 7:0  | Front tuning. 00: Coast start from 1 HSYNC lead 01: Coast start from 2 HSYNC lead 254: Coast start from 255 HSYNC 255: Coast start from 256 HSYNC                                                                                                                                                       | ling edge, default value. |  |

| 12h                                            | COCTRL3       | 7:0  | Default: 0x00                                                                                                                                                                                                                                                                                           | Access: R/W               |  |

|                                                | COEND[7:0]    | 7:0  | End tuning. 00: Coast end at 1 HSYNC leading edge. 01: Coast end at 2 HSYNC leading edge, default value 254: Coast end at 255 HSYNC leading edge. 255: Coast end at 256 HSYNC leading edge.                                                                                                             |                           |  |

| 13h                                            | VFAC_OINI     | 7:0  | Default: 0x00                                                                                                                                                                                                                                                                                           | Access : R/W              |  |

|                                                | VFACOINI[7:0] | 7:0  | Vertical Factor Odd Initial value.                                                                                                                                                                                                                                                                      |                           |  |

| 14h                                            | VFAC_EINI     | 7:0  | Default: 0x80                                                                                                                                                                                                                                                                                           | Access: R/W               |  |

|                                                | VFACEINI[7:0] | 7:0  | Vertical Factor Even Initial value                                                                                                                                                                                                                                                                      |                           |  |

| 15h                                            | -             | 7:0  | Default : -                                                                                                                                                                                                                                                                                             | Access: -                 |  |

|                                                | -             | 7:0  | Reserved.                                                                                                                                                                                                                                                                                               |                           |  |

| 16h                                            | INTCTROL      | 7:0  | Default: 0x00                                                                                                                                                                                                                                                                                           | Access: R/W               |  |

|                                                | CHG_HMD       | 7    | Change H Mode for INT.  0: Only in leading/tailing of CHG p  1: Every line generating INT pulse                                                                                                                                                                                                         |                           |  |

|                                                | -             | 6:4  | Reserved.                                                                                                                                                                                                                                                                                               |                           |  |

|                                                | IVSI          | 3    | Input VSYNC interrupt generated by 0: Leading edge. 1: Tailing edge.                                                                                                                                                                                                                                    | py:                       |  |

|                                                | OVSI          | 2    | Output VSYNC interrupt generated by: 0: Leading edge. 1: Tailing edge. Trigger Condition. 0: Active low for level trigger/tailing edge trigger. 1: Active high for level trigger/leading edge trigger. Interrupt Trigger. 0: Generate an edge trigger interrupt. 1: Generate a level trigger interrupt. |                           |  |

|                                                | TRGC          | 1    |                                                                                                                                                                                                                                                                                                         |                           |  |

|                                                | INT_TRIG      | 0    |                                                                                                                                                                                                                                                                                                         |                           |  |

| 17h                                            | INTPULSE      | 7:0  | Default : 0x0F                                                                                                                                                                                                                                                                                          | Access: R/W               |  |

|                                                | INTPULSE[7:0] | 7:0  | Interrupt Pulse width by reference of                                                                                                                                                                                                                                                                   | clock.                    |  |

| Scaler | Register (Bank=00, | Registers 0 | 01h ~ 9Fh)                                                                                                                                                                                                                                                          |              |

|--------|--------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Index  | Name               | Bits        | Description                                                                                                                                                                                                                                                         |              |

| 18h    | INTSTA             | 7:0         | Default: 0x00                                                                                                                                                                                                                                                       | Access: R/W  |

|        | INTSTA[7:0]        | 7:0         | Interrupt Status byte A. Bit 7: MVD input NOT "no signal". Bit 6: MVD "HSYNC lock". Bit 5: MVD NOT "no color". Bit 4: MVD degree error. Bit 3: MVD input "no signal". Bit 2: MVD NOT "HSYNC lock". Bit 1: MVD "no color". Bit 0: MVD HSYNC change.                  |              |

| 19h    | INTENA             | 7:0         | Default: 0x00                                                                                                                                                                                                                                                       | Access: R/W  |

|        | INTENA[7:0]        | 7:0         | Interrupt Enable control byte A. 0: Disable interrupt. 1: Enable interrupt.                                                                                                                                                                                         |              |

| 1Ah    | INTSTB             | 7:0         | Default: 0x00                                                                                                                                                                                                                                                       | Access: R/W  |

|        | INTSTB[7:0]        | 7:0         | Interrupt Status byte B. Bit 7: MCU D2B interrupt 2. Bit 6: MCU D2B interrupt 1. Bit 5: MCU D2B interrupt 0. Bit 4: MVD CC interrupt. Bit 3: MVD SECAM detect. Bit 2: MVD PAL switch error. Bit 1: MVD "ADC7_0ACT". Bit 0: MVD NOT "ADC7_0ACT".                     |              |

| 1Bh    | INTENB             | 7:0         |                                                                                                                                                                                                                                                                     | Access: R/C  |

|        | INTENB[7:0]        | 7:0         | Interrupt Enable control byte B. 0: Disable interrupt. 1: Enable interrupt.                                                                                                                                                                                         |              |

| 1Ch    | INTSTC             | 7:0         | Default: 0x00                                                                                                                                                                                                                                                       | Access : R/W |

|        | INTSTC[7:0]        | 7:0         | Interrupt Status byte C. Bit 7: Output VSYNC interrupt. Bit 6: Input VSYNC interrupt. Bit 5: ATG ready interrupt. Bit 4: ATP ready interrupt. Bit 3: ATS ready interrupt. Bit 2: MVD probe ready interrupt. Bit 1: MCU D2B interrupt 4. Bit 0: MCU D2B interrupt 3. |              |

| 1Dh    | INTENC             | 7:0         | Default: 0x00 Access: R/C                                                                                                                                                                                                                                           |              |

|        | INTENC[7:0]        | 7:0         | Interrupt Enable control byte C.  0: Disable interrupt.  1: Enable interrupt.                                                                                                                                                                                       |              |

| 1Eh    | INTSTD             | 7:0         | Default: 0x00                                                                                                                                                                                                                                                       | Access : R/W |

| Scaler | Register (Bank=00, F | Registers ( | <b>01h ~ 9Fh</b> )                                                                                                                                                                                                                                                                                         |                     |  |  |

|--------|----------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|

| Index  | Name                 | Bits        | Description                                                                                                                                                                                                                                                                                                |                     |  |  |

|        | INTSTD[7:0]          | 7:0         | Interrupt Status byte D. Bit 7: WDT interrupt. Bit 6: Keypad wake-up interrupt. Bit 5: Jitter interrupt. Bit 4: Horizontal total change interrupt. Bit 3: Vertical total change interrupt. Bit 2: Horizontal lost count interrupt. Bit 1: Vertical lost count interrupt. Bit 0: Standard change interrupt. |                     |  |  |

| 1Fh    | INTEND               | 7:0         | Default: 0x00                                                                                                                                                                                                                                                                                              | Access: R/C         |  |  |

|        | INTEND[7:0]          | 7:0         | Interrupt Enable control byte D 0: Disable interrupt. 1: Enable interrupt.                                                                                                                                                                                                                                 | ).                  |  |  |

| 20h ~  |                      | 7:0         | Default : -                                                                                                                                                                                                                                                                                                | Access : -          |  |  |

| 21h    | -                    | 7:0         | Reserved.                                                                                                                                                                                                                                                                                                  |                     |  |  |

| 22h    | MPL_M                | 7:0         | Default: 0x6F                                                                                                                                                                                                                                                                                              | Access: R/W         |  |  |

|        | MP_ICTRL[2:0]        | 7:5         | Charge pump current set.                                                                                                                                                                                                                                                                                   |                     |  |  |

|        | MPL_M[4:0]           | 4:0         | MPLL divider ratio setting.                                                                                                                                                                                                                                                                                |                     |  |  |

| 23h    | OPL_CTL0             | 7:0         | Default: 0x40                                                                                                                                                                                                                                                                                              | Access: R/W         |  |  |

|        | -                    | 7:6         | Reserved.                                                                                                                                                                                                                                                                                                  |                     |  |  |

|        | SSC_EN               | 6           | Output PLL spread spectrum. 0: Disable. 1: Enable.                                                                                                                                                                                                                                                         |                     |  |  |

|        | SD_MD                | 5           | Output PLL spread spectrum M. 0: Normal. 1: Reverse for mode 1.                                                                                                                                                                                                                                            | lode.               |  |  |

|        | -                    | 4:0         | Reserved.                                                                                                                                                                                                                                                                                                  |                     |  |  |

| 24h    | -                    | 7:0         | Default : -                                                                                                                                                                                                                                                                                                | Access: -           |  |  |

|        | -                    | 7:0         | Reserved.                                                                                                                                                                                                                                                                                                  |                     |  |  |

| 25h    | OPL_SET0             | 7:0         | Default: 0x44                                                                                                                                                                                                                                                                                              | Access : R/W, DB    |  |  |

|        | OPL_SET[7:0]         | 7:0         | Output PLL Set.                                                                                                                                                                                                                                                                                            |                     |  |  |

| 26h    | OPL_SET1             | 7:0         | Default: 0x55                                                                                                                                                                                                                                                                                              | Access : R/W, DB    |  |  |

|        | OPL_SET[15:8]        | 7:0         | See description for OPL_SET [                                                                                                                                                                                                                                                                              | [7:0].              |  |  |

| 27h    | OPL_SET2             | 7:0         | Default : 0x24                                                                                                                                                                                                                                                                                             | Access: R/W, DB     |  |  |

|        | OPL_SET [23:16]      | 7:0         | See description for OPL_SET [                                                                                                                                                                                                                                                                              | [7:0].              |  |  |

| 28h    | OPL_STEP0            | 7:0         | Default: 0x20                                                                                                                                                                                                                                                                                              | Access: R/W, DB     |  |  |

|        | OPL_STEP[7:0]        | 7:0         | Output PLL spread spectrum S                                                                                                                                                                                                                                                                               | tep.                |  |  |

| 29h    | OPL_STEP1            | 7:0         | Default: 0x00                                                                                                                                                                                                                                                                                              | Access: R/W, DB     |  |  |

|        | -                    | 7           | Reserved.                                                                                                                                                                                                                                                                                                  |                     |  |  |

|        | -                    | 6           | Reserved.                                                                                                                                                                                                                                                                                                  |                     |  |  |

|        | -                    | 5           | Reserved.                                                                                                                                                                                                                                                                                                  |                     |  |  |

|        | -                    | 4:3         |                                                                                                                                                                                                                                                                                                            | Reserved.           |  |  |

|        | OPL_STEP[10:8]       | 2:0         | See description for OPL_STEP                                                                                                                                                                                                                                                                               | <sup>2</sup> [7:0]. |  |  |

| Scaler | Register (Bank=00, R | egisters ( | 01h ~ 9Fh)                                                                                                                                                                                               |                                          |

|--------|----------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Index  | Name                 | Bits       | Description                                                                                                                                                                                              |                                          |

| 2Ah    | OPL_SPAN             | 7:0        | Default: 0x00                                                                                                                                                                                            | Access : R/W, DB                         |

|        | OPL_SPAN[7:0]        | 7:0        | Output PLL spread spectrum Sp                                                                                                                                                                            | pan.                                     |

| 2Bh    | OPL_SPAN             | 7:0        | Default: 0x00                                                                                                                                                                                            | Access : R/W, DB                         |

|        | READ_FRAME           | 7          | 0: OPL_SET stores line-based v<br>1: OPL_SET stores frame-based                                                                                                                                          |                                          |

|        | OPL_SPAN[14:8]       | 6:0        | See description for OPL_SPAN                                                                                                                                                                             | [7:0].                                   |

| 2Ch ~  | -                    | 7:0        | Default : -                                                                                                                                                                                              | Access: -                                |

| 2Fh    | -                    | 7:0        | Reserved.                                                                                                                                                                                                |                                          |

| 30h    | HSR_L                | 7:0        | Default: 0x00                                                                                                                                                                                            | Access : R/W                             |

|        | HSR [7:0]            | 7:0        | Horizontal Scaling ratio (20 bi (2^20-1)/2^20 (lower 8 bits).                                                                                                                                            | ts fraction) for scaling down 1/2^20 to  |

| 31h    | HSR_M                | 7:0        | Default: 0x00                                                                                                                                                                                            | Access: R/W                              |

|        | HSR[15:8]            | 7:0        | Horizontal Scaling ratio (20 bit (2^20-1)/2^20 (middle 8 bits).                                                                                                                                          | ts fraction) for scaling down 1/2^20 to  |

| 32h    | HSR_H                | 7:0        | Default: 0x00                                                                                                                                                                                            | Access: R/W                              |

|        | HS_EN                | 7          | Horizontal Scaling Enable.  0: Disable.  1: Enable.  Complemental Bi-Linear Enable.  0: Chrominance using same setting as Luminance defined CBILINEAR.  1: Chrominance always using bi-linear algorithm. |                                          |

|        | CBILINEAR_EN         | 6          |                                                                                                                                                                                                          |                                          |

|        | FORCEBICOLOR         | 5          |                                                                                                                                                                                                          |                                          |

|        | -                    | 4          | Reserved.                                                                                                                                                                                                | C                                        |

|        | HSR[19:16]           | 3:0        | Horizontal Scaling Ratio (20 bi (2^20-1)/2^20 (higher 8 bits).                                                                                                                                           | its fraction) for scaling down 1/2^20 to |

| 33h    | VSR_L                | 7:0        | Default: 0x00                                                                                                                                                                                            | Access: R/W                              |

|        | VSR[7:0]             | 7:0        | Vertical Scaling ratio (2 bits int to 1/2.9999 (lower 8 bits). xx.xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                                                                                                      | eger, 20 bits fraction) for scaling down |

| 34h    | VSR_M                | 7:0        | Default : 0x00                                                                                                                                                                                           | Access: R/W                              |

|        | VSR[15:8]            | 7:0        | Vertical Scaling ratio (2 bits int to 1/2.9999 (middle 8 bits). xx.xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                                                                                                     | eger, 20 bits fraction) for scaling down |